# 基于 VPX 的高性能计算机设计

李 宇,王 巍

(江苏自动化研究所, 江苏 连云港 222006)

摘要:为了解决基于并行总线结构的抗恶劣环境计算机计算性能不足的问题,提出了一种基于 VPX 的高性能抗恶劣环境计算机的设计方法;该方法中包括基于 VPX 的高性能抗恶劣环境计算机的设计思路和实现过程;在该方法采用了仿真与测试的手段保证了高速串行电路设计的正确性,采用水冷散热方式提高了计算机的散热效率;在设计完成后,在实验室环境下通过测试软件对计算机的功能进行了可靠性测试,通过示波器对关键高速信号进行了测试,在功能测试中计算机运行稳定可靠,关键高速信号参数满足规范要求。

关键词: VPX; 仿真; 高速串行; 计算机

# Design of High-performance Computer Based on VPX

Li Yu, Wang Wei

(Jiangsu Automation Research Institute, Lianyungang 222006, China)

Abstract: In order to solve the problem that parallel bus structure anti—harsh environment computer lack of computing performance, a design method of anti—harsh environment computer based on VPX is proposed. This method includes anti—harsh environment computer's design ideas and implementation of process. Simulation and test tools is used to ensure the accuracy of high—speed serial circuit design, water cooling ways is used to enhance the computer's cooling efficiency. After the design was completed, computer functions has been running for reliability test by software, critical high—speed signal is tested by the oscilloscope, the computer is stable and high—speed signal parameters meet key regulatory requirements in the test.

Key words: VPX; simulation; high-speed serial; computer

### 0 引言

随着技术的发展,要求抗恶劣环境计算机处理更大范围、更多来源、更高精度、更快速度的信息流,要求抗恶劣环境计算机处理速度持续提升。当前的抗恶劣环境计算机一般采用单核心处理器、低速并行总线接口,已逐渐无法满足应用的需求。

国外抗恶劣环境计算机已经通过采用多核多处理器技术和新的计算机体系结构来提升计算机的性能,这些技术促使抗恶劣环境计算机具有强大的计算处理能力,同时实现了多种数据流的高速/高带宽的总线数据传输。

VPX 规范是目前国际上最新的、兼容性最好的军用嵌入式计算机规范之一。VPX 高性能计算机是高性能、多处理、高速的 Fabric 交换式串行信息互连互通、可扩展的计算机系统。通过采用高性能多核处理器,构建基于 VPX 规范并行处理硬件平台,实现具有硬件功能逻辑备份和冗余特性的高性能密度计算机,实现高效和大量的数据计算,支持多个计算任务同时高效的运行[1-2]。

## 1 计算机组成原理

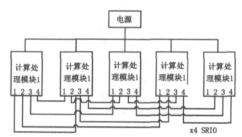

如图 1 所示,基于 VPX 的高性能计算机是主要由 5 块计

算处理模块组成,5块计算处理模块之间采用全网格互连。任意两个插槽之间存在高速串行物理连接通道,在这些通道可传输 PCI Express、RapidIO等信号。计算处理模块集成了1个高性能双核 PowerPC 处理器,该处理器集成高性能矢量处理引擎,计算处理模块彼此之间对外提供单独高速通道进行交互,在一个基于交换背板的机箱环境,最多可容纳 5 块同样的高性能密度计算模块,可构成一个强大的高性能计算机系统。

图 1 基于 VPX 的抗恶劣环境计算机组成原理框图

## 2 计算机处理模块设计

## 2.1 组成原理

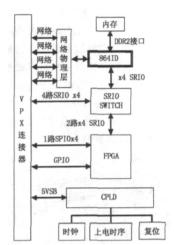

计算处理模块集成双核 MPC8641D 处理器,通过处理器 片上集成的各种接口,如 DDR2 控制器接口、网络 MAC 接 口、高速 SERDES 接口、LBC 接口分别实现 DDR2 存储器扩展、千兆以太网络、串行 SRIO 和 PCIe、Flash 存储器等接口。 板上集成一片 VIRTEX5 FPGA 作为协处理器,同时可进行 IO 接口功能扩展,SRIO 交换芯片 TSI568 提供 4 路 SRIO 到连接 器 P1,MPC8640D 处理器与 FPGA 分别有一个 SRIO 与之连

接,处理器和 FPGA 之间还可通过 LBC 接口连接。该处理模块对外可提供千兆以太网、串口、SRIO、PCIE 以及自定义的 IO 接口功能。

图 2 计算处理模块组成原理框图

#### 2.2 功能实现

CPU、FPGA、SRIO SWITCH 三部分的电源采用独立的电源芯片进行供电和控制,其中 CPU 部分所需的+3. 3V 通过公用的+3. 3V 和一个场效应管开关实现,+1. 8V 由独立的开关电源和 LDO 电源芯片实现,内核+1. 05V 由三相控制电源芯片实现,+2. 5V 通过公用获取;TSI568A 所需的内核+1. 2V、端接 VTT 均由独立的 LDO 电源芯片实现,IO 电压+3. 3V 由一个场效应管开关实现;FPGA 部分所需的内核电压、IO 电压、辅助电压以及各种端接电压均由独立的开关电源或LDO 电源芯片实现。通过将电源部分分开设计可以减少功能之间的耦合度,从而避免功能之间的相互影响,同时为了确保电源稳定可靠后输出给负载,在每个电源的输出端串接一个磁珠进行隔离方便电源调试。

时钟部分主要包括 CPU、TSI568A、FPGA 等,复位可以由上电复位、CPLD 控制复位、系统复位、手动复位。

包括 CPU 部分的 DDR2 存储器采用板子内存颗粒,每个 DDR2 控制器由 5 片独立芯片构成 64 位数据总线和 8 位 ECC,每个控制器接口实现 256MB,同时可以更换大容量的内存颗粒实现扩展,通过 LBC 接口实现 32MB 的 Flash 存储器。

#### 3 高速串行电路设计仿真与测试

VPX 计算机组成模块之间传输信号的频率一般在 GHz 级别,上升边沿为百分之一纳秒左右。因此这些信号属于高速串行信号,必须采取一定信号完整性设计才保证设计的一次成功率,同时测试手段和测试设备也需要同步更新,以便于硬件电路设计与验证的进行<sup>[3]</sup>。

### 3.1 高速串行电路设计仿真

高速串行电路设计仿真主要包括阻抗控制、损耗控制、串 扰控制 3 个方面。

### 3. 1. 1 阻抗控制

设计一个特定的特征阻抗,实际上就是不断调整线宽、介质厚度和介电常数的过程。

图 3 圆杆一平面型示意图

以如图 3 所表示的圆杆一平面型为例,其近似的特征阻抗的计算公式如下:

$$Z_0 = \frac{87\Omega}{\sqrt{1.41 + \epsilon_r}} \ln\left(\frac{5.98h}{0.8w + t}\right)$$

$Z_0$  表示特征阻抗,单位为  $\Omega$ ; h 表示信号线与平面间的介质厚度,单位 mil; w 表示线宽,单位 mil; h 表示平面间距,单位 mil; h 表示信号线金属层厚度,单位 mil; h 表示材料的介电常数。如果忽略信号线厚度 t 的影响,这两种结构的特征阻抗仅与介质厚度和线宽的比值有关。

印制板的叠层设计是控制阻抗、保证信号完整性的重要手段。该设计包括信号层和电地层的合理堆叠,叠层间的绝缘介质厚度控制等。合理叠层可为信号层提供了良好的参考平面,使信号完整性得以提升。在设计时,信号层尽可能与地平面相邻(确保关键信号层与地平面相邻); 电源层尽可能与其对应地层相邻;尽量避免两信号层直接相邻;兼顾层压结构对称。

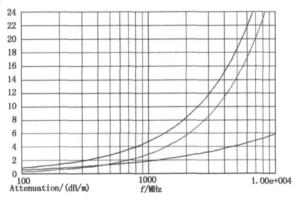

### 3. 1. 2 损耗仿真

图 4 是一个典型的损耗仿真结果,图中横坐标为频率,单位 MHz;纵坐标为损耗,单位是 dB/m。上面一根线代表衰减,中间的线代表介质损耗,下面的线代表导线损耗。将线宽设置为 3mil,这种极限的情况比较有代表性。

图 4 介质损耗仿真结果

从仿真的结果来看当信号频率在 1GHz 以下时,介质损耗效应还并不明显。但是当信号的频率超过 1GHz 后,介质损耗就必须被考虑了。

### 4.1.3 串扰仿真

串扰是多对信号之间存在的主要信号完整性问题。如图 5 所示,串扰的仿真结果表明,差分传输线的耦合长度 5inch,差分线之间的间距为 30,所有线都在表层。当通道 1 传输时,通道 2 上的串扰达到 46mv。该串扰值比较大,需要采取措施抑制串扰。改善串扰一般有两个手段,增大线间距和减少耦合长度。

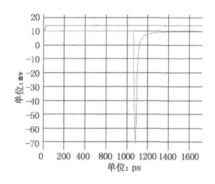

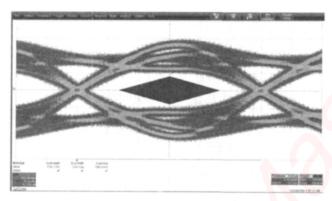

#### 3.2 高速串行电路测试

眼图是测量高速信号抖动性能的重要测试手段,通过使用

图 5 串扰仿真结果

完整的时钟恢复功能、抖动分离算法和误码率估算功能的进一步增强,示波器已经成为检定和降低定时抖动的唯一解决方案<sup>[4]</sup>。由于 SRIO 的信号速率比较高,因此要对 SRIO 信号进行可靠的探测,对于示波器和探头的要求也非常高。SRIO 信号的测试主要是参照可以参考电气规范上关于一致性测试的要求。对于  $2.5 \, \mathrm{GHz}$  频率的 SRIO 信号的测试需要示波器的带宽是  $6 \, \mathrm{GHz}$ 。

图 6 测试眼图

图 7 液冷机箱组成示意图

# 4 液冷散热设计

基于 VPX 的抗恶劣环境计算机,体积结构上仍沿袭了ATR、19 英寸上架机箱等设计理念。多核处理器高密度设计和多处理模块高度集成,传统的散热技术将很难适用。针对功耗增加,国外计算机协会已于 2006 年公布了新的计算机导冷技术规范—— 液冷技术规范 VITA48。

如图 7 液冷计算机系统由内外设备组成,当使用者启动液压泵 1 时,液压泵便加压冷却液。冷却液通过进水管 2、进水口进入到液冷散热模块冷板的液冷散热模块水腔 4,并在液冷

散热模块水腔处流动的过程中,可与 6U 印制板的热源产生热交换。经过热交换的冷却液通过出水口、出水管回到冷却泵,从而完成一次散热循环。

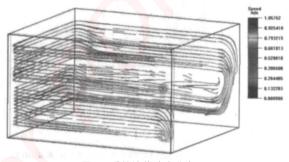

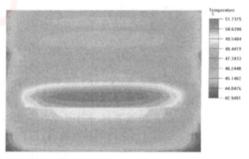

利用 Icepak 软件进行热控制方案数据分析,通过仿真分析和理论计算,验证系统的换热能力,论证液冷管路分布的合理性,同时获得水道单位体积流量和系统压力损失值,为确立外部热交换系统技术参数提供依据,从而完成整个机箱的热循环设计。可得系统内部速度分布及左壁温度云图如下:此工况下的系统单位体积流量为  $0.248\mathrm{CFM}$  ( $\approx 0.000117\mathrm{m}^3/\mathrm{s}$ ),进出口压力损失为  $1839\mathrm{Pa}$ ,内壁最高温度为  $51.74\mathrm{C}$ ,平均温度为  $48.1\mathrm{C}$ ,冷却剂进出温差为  $1.9\mathrm{C}$ 。

图 8 系统流体速度分布

图 9 水冷机箱左壁内侧温度分布云图

#### 5 结束语

基于 VPX 的高性能抗恶劣环境计算机按照 VPX 规范,采用基于双核高性能 PowerPC 处理器的计算机处理模块组成了高性能计算机系统,同时采用液冷技术保证了计算机性能的实现。基于 VPX 的高性能抗恶劣环境计算机的设计方法已经成功的应用,在应用过程中性能稳定、效果良好。

#### 参考文献:

- [1] 郑东卫,陈 矛,罗丁利. VPX 总线的技术规范及应用 [J]. 火控 雷达技术,2009,(04):73-77.

- [2] 杨光灿, 黄钰林, 杨建宇. 基于 VPX 标准的 SAR 实时信号处理板设计 [J]. 电讯技术, 2009, (12): 39-42.

- [3] 王学宝. 基于 VPX 标准的 PMC/XMC 载板设计 [J]. 计算机测量与控制, 2010(8): 1852-1855.

- [4] 王学宝,陈海荣. 基于 DVI 的差分电路仿真测试研究 [J]. 计算机测量与控制,2010,(11):2488-2490.

# 嵌入式资源免费下载

# 总线协议:

- 1. 基于 PCIe 驱动程序的数据传输卡 DMA 传输

- 2. 基于 PCIe 总线协议的设备驱动开发

- 3. CANopen 协议介绍

- 4. 基于 PXI 总线 RS422 数据通信卡 WDM 驱动程序设计

- 5. FPGA 实现 PCIe 总线 DMA 设计

- 6. PCI Express 协议实现与验证

- 7. VPX 总线技术及其实现

- 8. 基于 Xilinx FPGA 的 PCIE 接口实现

- 9. 基于 PCI 总线的 GPS 授时卡设计

- 10. 基于 CPCI 标准的 6U 信号处理平台的设计

- 11. USB30 电路保护

- 12. USB30 协议分析与框架设计

- 13. USB 30 中的 CRC 校验原理及实现

- 14. 基于 CPLD 的 UART 设计

- 15. IPMI 在 VPX 系统中的应用与设计

- 16. 基于 CPCI 总线的 PMC 载板设计

- 17. 基于 VPX 总线的工件台运动控制系统研究与开发

- 18. PCI Express 流控机制的研究与实现

- 19. UART16C554 的设计

# VxWorks:

- 1. 基于 VxWorks 的多任务程序设计

- 2. 基于 VxWorks 的数据采集存储装置设计

- 3. Flash 文件系统分析及其在 VxWorks 中的实现

- 4. VxWorks 多任务编程中的异常研究

- 5. VxWorks 应用技巧两例

- 6. 一种基于 VxWorks 的飞行仿真实时管理系统

- 7. 在 VxWorks 系统中使用 TrueType 字库

- 8. 基于 FreeType 的 VxWorks 中文显示方案

- 9. 基于 Tilcon 的 VxWorks 简单动画开发

- 10. 基于 Tilcon 的某武器显控系统界面设计

- 11. 基于 Tilcon 的综合导航信息处理装置界面设计

- 12. VxWorks 的内存配置和管理

- 13. 基于 VxWorks 系统的 PCI 配置与应用

- 14. 基于 MPC8270 的 VxWorks BSP 的移植

- 15. Bootrom 功能改进经验谈

- 16. 基于 VxWorks 嵌入式系统的中文平台研究与实现

- **17**. VxBus 的 A429 接口驱动

- 18. 基于 VxBus 和 MPC8569E 千兆网驱动开发和实现

- 19. 一种基于 vxBus 的 PPC 与 FPGA 高速互联的驱动设计方法

- 20. 基于 VxBus 的设备驱动开发

# Linux:

- 1. Linux 程序设计第三版及源代码

- 2. NAND FLASH 文件系统的设计与实现

- 3. 多通道串行通信设备的 Linux 驱动程序实现

- 4. Zsh 开发指南-数组

- 5. 常用 GDB 命令中文速览

- 6. 嵌入式 C 进阶之道

- 7. Linux 串口编程实例

- 8. 基于 Yocto Project 的嵌入式应用设计

- 9. Android 应用的反编译

- 10. 基于 Android 行为的加密应用系统研究

- 11. 嵌入式 Linux 系统移植步步通

- 12. 嵌入式 CC++语言精华文章集锦

- 13. 基于 Linux 的高性能服务器端的设计与研究

- 14. S3C6410 移植 Android 内核

- 15. Android 开发指南中文版

- 16. 图解 Linux 操作系统架构设计与实现原理(第二版)

- 17. 如何在 Ubuntu 和 Linux Mint 下轻松升级 Linux 内核

- 18. Android 简单 mp3 播放器源码

- 19. 嵌入式 Linux 系统实时性的研究

- 20. Android 嵌入式系统架构及内核浅析

# Windows CE:

WeChat ID: kontronn

- 1. Windows CE. NET 下 YAFFS 文件系统 NAND Flash 驱动程序设计

- 2. Windows CE的 CAN 总线驱动程序设计

- 3. 基于 Windows CE. NET 的 ADC 驱动程序实现与应用的研究

- 4. 基于 Windows CE. NET 平台的串行通信实现

- 5. 基于 Windows CE. NET 下的 GPRS 模块的研究与开发

- 6. win2k 下 NTFS 分区用 ntldr 加载进 dos 源代码

- 7. Windows 下的 USB 设备驱动程序开发

- 8. WinCE 的大容量程控数据传输解决方案设计

- 9. WinCE6.0 安装开发详解

- 10. DOS 下仿 Windows 的自带计算器程序 C 源码

- 11. G726 局域网语音通话程序和源代码

- 12. WinCE 主板加载第三方驱动程序的方法

- 13. WinCE 下的注册表编辑程序和源代码

- 14. WinCE 串口通信源代码

- 15. WINCE 的 SD 卡程序[可实现读写的源码]

- 16. 基于 WinCE 的 BootLoader 研究

# PowerPC:

- 1. Freescale MPC8536 开发板原理图

- 2. 基于 MPC8548E 的固件设计

- 3. 基于 MPC8548E 的嵌入式数据处理系统设计

- 4. 基于 PowerPC 嵌入式网络通信平台的实现

- 5. PowerPC 在车辆显控系统中的应用

- 6. 基于 PowerPC 的单板计算机的设计

- 7. 用 PowerPC860 实现 FPGA 配置

# ARM:

- 1. 基于 DiskOnChip 2000 的驱动程序设计及应用

- 2. 基于 ARM 体系的 PC-104 总线设计

- 3. 基于 ARM 的嵌入式系统中断处理机制研究

- 4. 设计 ARM 的中断处理

- 5. 基于 ARM 的数据采集系统并行总线的驱动设计

WeChat ID: kontronn

- 6. S3C2410 下的 TFT LCD 驱动源码

- 7. STM32 SD 卡移植 FATFS 文件系统源码

- 8. STM32 ADC 多通道源码

- 9. ARM Linux 在 EP7312 上的移植

- **10.** ARM 经典 300 问

- 11. 基于 S5PV210 的频谱监测设备嵌入式系统设计与实现

- 12. Uboot 中 start. S 源码的指令级的详尽解析

- 13. 基于 ARM9 的嵌入式 Zigbee 网关设计与实现

# Hardware:

- 1. DSP 电源的典型设计

- 2. 高频脉冲电源设计

- 3. 电源的综合保护设计

- 4. 任意波形电源的设计

- 5. 高速 PCB 信号完整性分析及应用

- 6. DM642 高速图像采集系统的电磁干扰设计

- 7. 使用 COMExpress Nano 工控板实现 IP 调度设备

- 8. 基于 COM Express 架构的数据记录仪的设计与实现