本篇主要讲述了PCIe配置对性能的影响

PCIe用途

当PCIe 应用于网卡和主机间通信时,网络适配器需要与 CPU 和内存(以及其他模块)进行通信。这意味着为了处理网络流量,应该对通过 PCIe 进行通信的不同设备进行良好配置。将网络适配器连接到 PCIe 时,它会自动协商网络适配器和 CPU 之间支持的最大功能。

PCIe 属性

任何 PCI 设备都加载了某些属性。其中一些属性对性能至关重要。设备的 PCIe 属性是通过系统和设备能力之间的协商来设置的。这导致两者都可以支持被选择的最高值。下面,您可以找到相关 PCIe 属性的说明、如何验证它们以及它们对性能的影响。

PCIe 宽度

PCIe 宽度决定了设备可并行用于通信的 PCIe 通道数。宽度标记为 xA,其中 A 是通道数(例如,x8 表示 8 通道)。具体支持多少通道取决于厂商的设备和它们的型号。为了验证 PCIe 宽度,可以使用命令 lspci。

在本例中,我们在 PCI 04.00.0 地址上安装了 Mellanox 适配器。

# lspci -s 04:00.0 -vvv | grep Width

LnkCap: Port #0, Speed 8GT/s, Width x8, ASPM not supported, Exit Latency L0s unlimited, L1 unlimited

LnkSta: Speed 8GT/s, Width x8, TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt-

如您所见,PCIe 报告了已通信的设备功能(在 LnkCap 下),以及它们的当前状态(在 LnkSta 下),这是实际的 PCIe 设备属性。

PCIe 速度

确定可能的 PCIe 事务数。速度以 GT/s 为单位,代表“每秒十亿次交易”。与 PCIe 宽度一起确定了最大 PCIe 带宽(速度 * 宽度)。为了验证 PCIe 速度,可以使用命令 lspci。

# lspci -s 04:00.0 -vvv | grep Speed

LnkCap: Port #0, Speed 8GT/s, Width x8, ASPM not supported, Exit Latency L0s unlimited, L1 unlimited

LnkSta: Speed 8GT/s, Width x8, TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt

与宽度参数类似,设备能力和状态都会被报告。

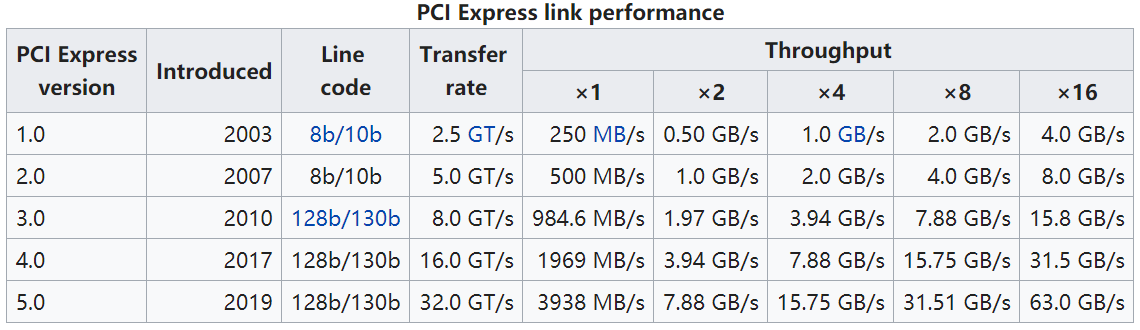

PCIe 速度被标识为“代”,其中 2.5GT/s 称为“gen1”,5GT/s 称为“gen2”,8GT/s 称为“gen3”,16GT/s 称为“gen4”。

注意:除了支持的速度之外,各代之间的主要区别在于数据包的编码开销。对于第 1 代和第 2 代,在 PCIe 上发送的每个数据包都有 20% 的 PCIe 标头开销。这在第 3 代中得到了改进,其中开销减少到 1.5% (2/130)。有关更多详细信息,请参阅下面的实际 PCIe 带宽计算。

PCIe Max Payload Size

PCIe Max Payload Size 确定 PCIe 数据包或 PCIe MTU 的最大大小(类似于网络协议)。这意味着较大的 PCIe 事务被分解为 PCIe MTU 大小的数据包。此参数仅由系统设置,取决于芯片组架构(例如 x86_64、Power8、ARM 等)。您可以使用命令 lspci(在 DevCtl 下指定)查看 PCIe Max Payload Size。

lspci -s 04:00.0 -vvv | grep DevCtl: -C 2

DevCap: MaxPayload 512 bytes, PhantFunc 0, Latency L0s unlimited, L1 unlimited

ExtTag+ AttnBtn- AttnInd- PwrInd- RBE+ FLReset+

DevCtl: Report errors: Correctable- Non-Fatal+ Fatal+ Unsupported-

RlxdOrd+ ExtTag+ PhantFunc- AuxPwr- NoSnoop+ FLReset-

MaxPayload 256 bytes, MaxReadReq 4096 bytes

PCIe Max Read Request

PCIe Max Read Request 确定允许的最大 PCIe 读取请求。由于必须为传入响应准备缓冲区,PCIe 设备通常会跟踪待处理的读取请求的数量。PCIe 最大读取请求的大小可能会影响待处理请求的数量(当使用大于 PCIe MTU 的数据获取时)。同样,使用命令 lspci 来查询 Max Read Request 值。

# lspci -s 04:00.0 -vvv | grep MaxReadReq

MaxPayload 256 bytes, MaxReadReq 4096 bytes

与此处讨论的其他参数相反,可以在运行时使用命令 setpci 更改 PCIe Max Read Request:首先,查询该值以避免覆盖其他属性:

# setpci -s 04:00.0 68.w

5936

第一个数字是 PCIe Max Read Request。设置选Max Read Request:

# setpci -s 04:00.0 68.w=2936

该值应使用命令 lspci 更新:

# lspci -s 04:00.0 -vvv | grep MaxReadReq

MaxPayload 256 bytes, MaxReadReq 512 bytes

可接受的值为:0 -128B、1 - 256B、2 - 512B、3 - 1024B、4 - 2048B 和 5 - 4096B。

计算 PCIe 带宽限制

如前所述,PCIe 功能可能会影响网络适配器的性能。最好了解 PCIe 引入的带宽限制。下面是理论计算和几个例子。

最大可能的 PCIe 带宽是通过乘以 PCIe 宽度和速度来计算的。从这个数字中,我们减少了大约 1Gb/s 的纠错协议和 PCIe 标头开销。开销由 PCIe 编码(有关详细信息,请参阅 PCIe 速度)和 PCIe MTU 确定:

最大 PCIe 带宽 = 速度 * 宽度 * (1 - 编码) - 1Gb/s。

例如,具有 x8 宽度的第 3 代 PCIe 设备将被限制为:

最大 PCIe 带宽 = 8G * 8 * (1 - 2/130) - 1G = 64G * 0.985 - 1G = ~62Gb/s。

另一个示例 - 具有 x16 宽度的第 2 代 PCIe 设备将被限制为:

最大 PCIe 带宽 = 5G * 16 * (1 - 1/5) - 1G = 80G * 0.8 - 1G = ~63Gb/s。

注意:PCIe 事务包括网络数据包有效负载和标头,因此在计算网络流量的 PCIe 限制时需要考虑它们。

PCIe Max Read Request 和 Max Payload Size 可能会由于 PCIe 整体增加和相同负载的待处理事务而导致事务速率限制。