- 说明

- 点击数:658

贴片电阻,相信对于硬件研发工程师或者采购工程师而言并不会感到陌生;在众多型号参数的贴片电阻中,有一个电阻比较特殊,也就是本文介绍的主角---0欧姆电阻;由于其电阻阻值特殊,因此在项目的电路设计中经常被用于一些特殊的应用场景;那么对于0欧姆电阻,存在哪些电路设计技巧呢?

0欧姆电阻电路设计:

- 说明

- 点击数:2800

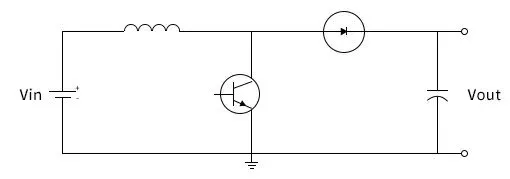

Boost电路是一种开关直流升压电路,它能够使输出电压高于输入电压。在电子电路设计当中算是一种较为常见的电路设计方式。本文将给大家介绍boost基本原理、电路参数设计。

首先我们需要知道:

- 电容阻碍电压变化,通高频,阻低频,通交流,阻直流;

- 电感阻碍电流变化,通低频,阻高频,通直流,阻交流;

图1Boost开关升压电路的原理图

假定那个开关(三极管或者MOS管)已经断开了很长时间,所有的元件都处于理想状态,电容电压等于输入电压。

下面要分充电和放电两个部分来说明这个电路。

- 说明

- 点击数:1106

RTL仿真无法仿真出CDC 问题或其影响。门级仿真是感知延迟的,但是它们只能在项目的后期执行。

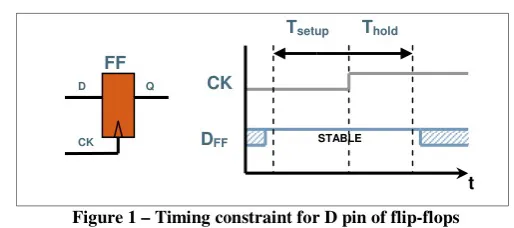

跨时钟域(CDC)路径的终点是触发器,由于时钟的不同步,该触发器可能进入危险的亚稳态。

当这些时序不被满足时(即D上的toggle发生在CK边沿太近)时,触发器输出的行为是不可预测的:输出可能是亚稳态,这意味着在0和1之间以一定的水平振荡。这种振荡应该在一定时间后最终稳定在0或1。

在异步设计中,没有办法保证满足setup和hold timing。因此,设计必须能够抵抗这些因素的影响,即避免亚稳态对后续逻辑的影响。

- 说明

- 点击数:1244

“波峰焊”与“回流焊”是电子产品制造中的两大关键焊接技术。这两种方法在焊接原理、操作流程以及所适用元件类型上均有所不同。接下来,我们将深入探讨这两者的共性与差异。

首先,让我们了解一下“波峰焊”。这一技术最初是在印刷电路板(PCB)的焊接中得以应用。在自动化技术普及之前,焊接工作主要依赖人工完成,左手焊锡丝,右手电烙铁,这成为了许多半导体从业者的共同记忆。然而,随着工厂生产的机械化程度不断提高,波峰焊技术逐渐崭露头角。这种焊接方法主要适用于需要插件焊接的场景,如将器件的引脚插入通孔中。

随后,印刷电路板(PCB)通过传送带被精准地输送到熔融锡水槽的上方。

- 说明

- 点击数:765

在现实世界中,电子电路所处的周围环境总是变幻莫测的。人体静电、雷击浪涌、误操作等诸多不可预料的因素时刻威胁着电子设备的正常工作。因此保护电路的作用与意义非常重要。经过多年的发展,保护电路从最简单的保险丝一步一步发展到现如今纷繁复杂的各种器件,它们分别承担着不同的作用。

1、短路保护

短路保护电路的主要作用是当电路系统中发生短路情况时及时断开闭合电路以此保证后续各个器件的安全。

当电源系统发生短路时,电路中的电流会瞬间增大到正常状况的好几倍甚至十多倍。我们可以利用这个特性,在电路中串入保险丝。当电流增大到保险丝的熔断电流时,保险丝会因为自身过热而发生熔断从而断开电路,这是最常见的保护电路之一。

但是这种保险丝有一个缺点:当保险丝熔断之后,必须由工程人员排除故障之后手动替换新的保险丝,这在一些狭小空间等场合十分不便,因此后来便诞生了“自恢复保险丝”。这种保险丝在发生熔断之后随着温度的降低又会重新接通,这样便可以在发生故障时断开供电开关,等排查故障之后再打开供电开关即可。自恢复保险丝是如何做到“自恢复”的呢?

自恢复保险丝,是由经过特殊处理的聚合树脂及分布在里面的导电粒子组成。

在正常状况下,聚合树脂紧密地将导电粒子束缚在结晶状的结构外,构成链状导电电通路,此时的自恢复保险丝为低阻状态,线路上流经自恢复保险丝的电流所产生的热能小,不会改变晶体结构。当线路发生短路或过载时,流经自恢复保险丝的大电流,产生的热量使聚合树脂融化,体积迅速增长,形成高阻状态,工作电流迅速减小,从而对电路进行限制和保护。因此由自恢复保险丝构成的保护电路还可以承担过热过流保护。

© 2026 VxWorks Club