- 说明

- 点击数:1544

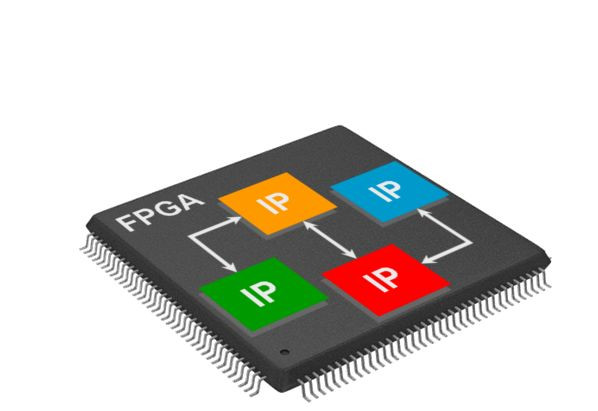

FPGA(现场可编程门阵列)是一种高度灵活的集成电路,它的设计允许用户在现场进行硬件功能的配置和定制。简单来说,FPGA 就像是一个可以在“上机”后重新编程的电路板,它不像传统的固定功能芯片(如微处理器),而是一个能够根据需求动态重新配置的硬件平台。

1. FPGA的核心组成

FPGA的工作原理基于两个主要组件:可编程逻辑单元(CLB,Configurable Logic Block)和可编程互连结构。

CLB(可编程逻辑块):CLB是FPGA的核心,它类似于一块“积木”,通过不同的配置可以完成各种不同的逻辑功能。每个CLB主要由以下几个部分组成:

查找表(LUT,Look-Up Table):查找表是FPGA中用于存储逻辑函数的模块,它通过存储一系列预设的输入-输出对应关系,来实现复杂的逻辑运算。你可以把它看作是一个小型的真值表,根据输入值查找输出。

多路复用开关(Multiplexer):用于根据不同条件选择不同的输入信号。

触发器(Flip-Flop):用于存储信号的状态,通常用来保持数据或者同步信号。

可编程互连结构:FPGA内部包含大量的连接线路,可以根据设计的需求进行重新配置。这些线路可以连接不同的CLB和模块,实现数据的传输和信号的路由。

- 说明

- 点击数:1835

1、Verilog语法基础

在Verilog中,端口的声明通常位于模块的端口列表中。输入端口使用input关键字,输出端口使用output关键字。

例如:

module my_module(

input wire clk, // 时钟输入

output wire rst // 复位信号输出

);

endmodule

- 说明

- 点击数:1382

CPU和GPU都属于冯·诺依曼结构,指令译码执行,共享内存。FPGA之所以比CPU、GPU更快,本质上是因为其无指令,无共享内存的体系结构所决定的。

冯氏结构中,由于执行单元可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。而FPGA的每个逻辑单元的功能在重编程时就已经确定,不需要指令。

冯氏结构中使用内存有两种作用:①保存状态。②执行单元间的通信。

- 保存状态:FPGA中的寄存器和片上内存(BRAM)是属于各自的控制逻辑的,无需不必要的仲裁和缓存。

- 通信需求:FPGA每个逻辑单元与周围逻辑单元的连接在重编程时就已经确定了,并不需要通过共享内存来通信。

计算密集型任务中:

- 说明

- 点击数:1468

摘 要:

提出一种基于现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)的超转保护系统设计方案。该系统采用三余度采集、控制架构,通过软件及逻辑表决控制单元及BIT检测单元,进一步提升了超转保护系统的可靠性。相较于传统的基于CPU的转速采集系统,其具备并行处理、运算速度快、功耗低、实时性强等特点,同时能释放大量CPU资源。该设计具备较强的通用性和实用性,对应急动力装置电子控制单元的超转保护系统设计具有一定的参考借鉴意义。

关键词:

应急动力装置;超转保护逻辑;BIT设计

0 引言

应急动力装置是以燃料分解产生的热燃气或发动机引气为动力源的涡轮动力装置[1],由涡轮、燃烧分解室、燃料箱、齿轮箱及控制部件组成,可以在发动机故障、主电源故障或主液压源故障时,通过开关指令快速启动,为飞机提供应急电源和液压源[2]。为了保证涡轮动力装置及其负载的安全可靠运转,必须可靠地监测涡轮轴转速,并据此快速、准确地控制相应执行机构的开关时机或开度大小,以保证涡轮轴转速稳定在允许范围内[3-4]。

超转保护功能作为应急动力装置必要的安全功能之一,是实现转速稳定控制的前提保证。本文提出了一种基于现场可编程逻辑门阵列的超转保护系统,通过设计多通道并行采集、软件与逻辑独立、并行控制及BIT测试功能,具备高可靠性、强实时性等特点,可保证在超转故障初期进行有效的隔离保护,从而降低单点故障和共模故障造成的应急动力装置转速控制失效的风险,避免造成涡轮装置结构损伤及飞行安全[5]。

- 说明

- 点击数:1691

本文主要介绍CPLD和FPGA的区别。

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。CPLD的LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数增长。FPGA的LAB以网格阵列排列,随器件密度线性增长。CPLD互连包括LAB本地可编程阵列及中心可编程互连。FPGA器件除了包括本地互连,用于各个LAB,但是和LAB逻辑分开,器件还包括行列互连,这些互连跨过阵列中的多个LAB,以及整个芯片的长宽。

© 2026 VxWorks Club