fpga设计属于IC设计中的一个分支,在IC设计过程中,占据重要的地位。下面给出一种在FPGA中,高速串行数据流的一种处理方法。

基本原理

高速串行数据流数据处理主要包括以下几个部分:

过采样:以高速时钟对串行数据比特流进行采样,一般取4倍或以上时钟(根据选择FPGA器件进行时钟速率选取);

数据修正:对过采样的数据进行修正,目的是适应收发双方频差,使得接收方能够正确解析数据、按照标称时钟速率还原接收串行数据;

边沿对齐:根据信号编码方式进行边沿数据处理,如NRZI编解码/曼彻斯特编解码,不同编码处理其处理方式各有不同;

串-并转换:根据数据帧概念完成串行数据到并行数据转换,进行数据帧解析。

数据过采样

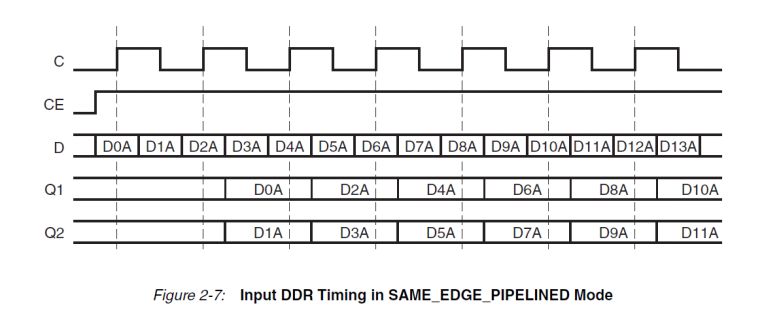

以xilinx器件为例,接收方主要采取IDDR/ISERDERS2源语进行数据过采样,工作模式采取SAME_EDGE_PIPELINED工作模式,采取4倍频采样。

实施步骤:

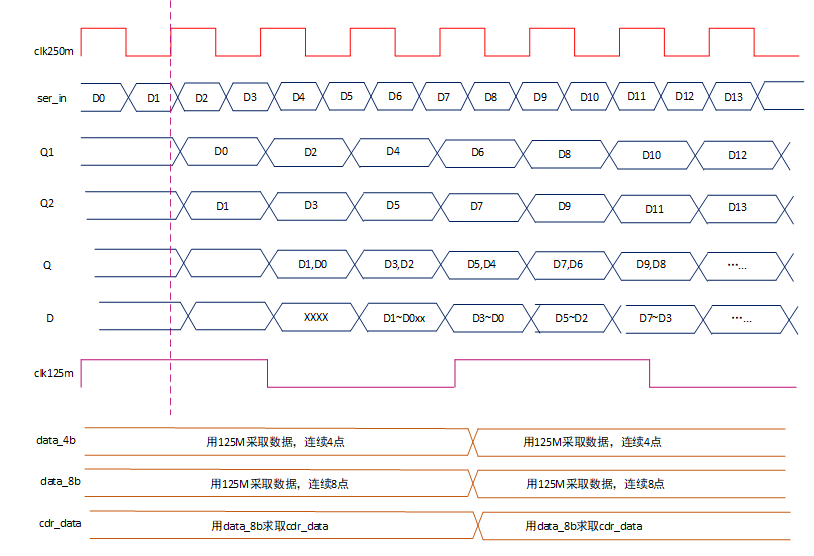

- 以CLK2X时钟上下边沿对串行数据进行4倍采样;

- 以CLK2X对采样数据进行移位,得到连续4点串行数据;

- 以CLKX单边沿采样完成4倍频数据向CLKX时钟域下的转变,得到CDR_DATA;遇到FT3/串口(串口速率非常低,可不使用次方法)这种串行数据流不是特别高的情况,可以采用更高的数据采样后进行数据抽取降采样。

数据修正

实施步骤:

- 在CLKX时钟域下,CDR通过移位形成CDR_8 B数据;

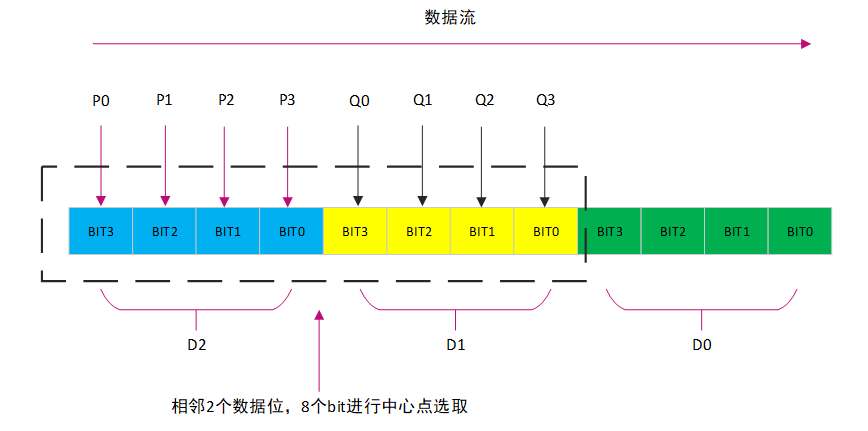

- 选点位置规则:从连续不断的串行数据流中取数据,设定选取位置bit_pos只能为0,1,2,3。假设数据流如上图所示,右边为老数据,左边为新数据,每次从D2的4个bit中取数,假设BIT0对应位置为3,BIT1对应位置2,BIT2对应位置1,BIT3对应位置0,位置判定规则如下(代码1):

- 调相选点:当BIT_POS=1时,进入调相选点状态。由于收发双方频差造成位置选定不可能一直为1,需要根据接收中心位置进行动态调整,调整规则如下: 当BIT_POS_DLY=3而BIT_POS=0时,表明数据上次选取数据和此次选取数据相邻,造成数据重复;当BIT_POS_DLY=0而BIT_POS=3时,表明此次选取数据和上次选取数据相隔较远,造成中间数据有丢失,需要补点,补点上次的点,即为中间点。(备注:当数据流反向时,上面补点和丢点的顺序正好相反。)

- 数据缓存:由于收方双方频率不一致,丢点补点后采取小型FIFO进行数据缓存。

- 缓存后的数据送往下一级进行数据边沿对齐处理。

代码1

if (P0 ^P1==1) bit_pos <= 2’d0 ;

else if (P1^P2==1) bit_pos <= 2’d3 ;

else if (P2^P3==1) bit_pos <= 2’d2 ;

else if (P3^Q0==1) bit_pos <= 2’d1 ;

边沿对齐及首字符界定

实施步骤:根据信号编码方式进行不同处理,NRZI进行相邻数据异或;曼码采取和时钟异或,处理比较简单,此处不再赘述。然后根据信号帧格式利用帧头或者帧首界定符进行判断,状态机处理比较简单,不再赘述。根据首字符实现串并转换。

通过上述方法已经成功实现常见FT3编码已经100M以太NRZI编码后的处理(无PHY),实现商用处理。