将图像处理的算法转换为FPGA系统设计的过程称为算法映射,CPU并行算法的实现与FPGA并行算法的实现是有一定区别的。

1. 算法系统结构

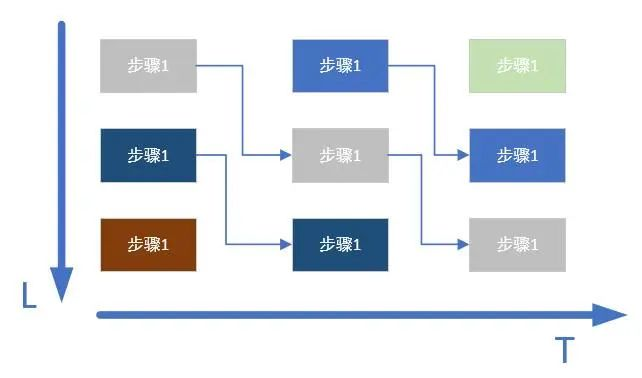

图像处理算法主要有两种设计结构:流水线结构和并行阵列结构。

1.1 流水线结构

在我看来,流水线结构和我们之前所理解的CPU的串行结构还是有一定区别的。相反,它与处理器的流水线结构很相似,都是依照时钟来进行流水层级的同步。

1.2 并行阵列结构

|--Data1--->Data1-->Data1

|

InputData------Data2--->Data2-->Data2

|

|--Data3--->Data3-->Data3

2.算法转换

2.1 定常数转换

对于FPGA而言,做加法与移位较为简单,而涉及到乘法与除法时需要调用到乘法器或除法器,这在FPGA中是较为宝贵的资源,所以作为定常数,我们尽量转换为移位和加法运算,如:

ex1:

dout = din * 255

转换后

dout = ( din << 8 ) - din

ex2:

dout = din * 11

转换后:

dout = din * 2^2 + din * 2^3 - din * 2^0

= din * (2^2 + 2^3 - 2^0)

上式中的255 和 11就是定常数

2.2 不等式等效转换

进行转换的目的也是为了在FPGA实现后能够更加节省资源。如:

ex1:

√a ̄ < b, a > 0

转换后:

b^2 > a

ex2:

a/b > c/b (b > 0, d > 0)

转换后

a * d > b * c

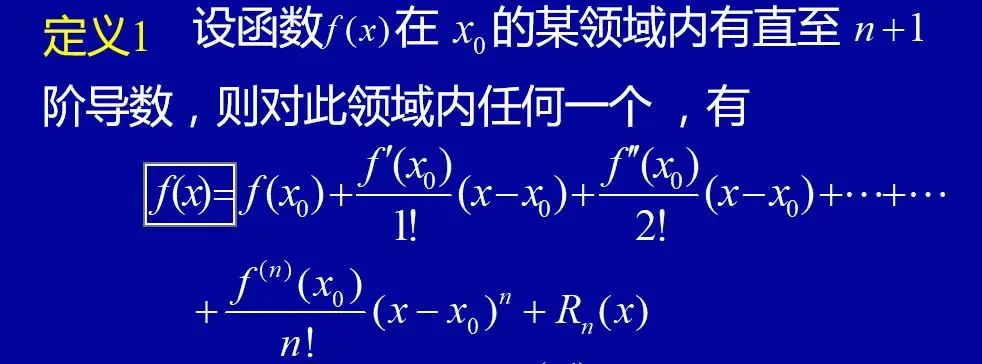

2.3 取近似值

最简单的近似值莫过于四舍五入,假如某数据D[-1~4]为整数部分,D[3~0]为小数部分,那么四舍五入可为:

assign dout = din[3]?(dout[-1~4] + 1) : (dout[-1~4])

泰勒公式定义

那么就可以有如下近似转换:

1/3 = 1/4 * (1 + 1/4 + 1/16 + 1/64 + 1/256)

3. 构造查找表

查找表是使用简单的查询操作代替运行时的实时计算,使用查找表代替那些运行时经常需要用到的运算能够极大的减少时间复杂度,如我们经常用到的三角函数就应该使用查找表替换实时计算。