机载产品通常系统复杂,功能单元众多,实现国产化周期长、难度大。FPGA是一种通过编程改变逻辑功能的半定制芯片,具有编程配置灵活、开发周期短等特点,为机载产品国产化提供了新思路。鉴于此,深入研究了CAN总线通信协议,分析了CAN驱动的数据流和组织结构,实现了基于FPGA的SJA1000 CAN总线驱动设计,并将该设计应用于某综合电子战管理系统,证实了其有效性和可靠性。

FPGA; CAN总线; 驱动设计

0 引言

随着嵌入式系统互联通信的高速发展,传统的RS232、RS485、RS422等总线受传输距离、抗干扰能力、负载能力、传输速率的影响,逐渐制约了嵌入式系统的发展。

CAN总线系统是一种多主控的总线系统,在总线控制器的协调下实现两个节点之间大量数据的传输,由于CAN网络消息的发送是广播式的,即所有节点侦测的数据是一致的,因此非常适合控制信息和数据信息的传输[1-2]。

CAN总线具有超长的传输距离,理论上限为10 km,因此被广泛应用于超远距离信息传输的工业项目中。单条总线可负载110个节点,互不干扰;高波特率保证了数据传输速率[3]。

由于国产化需求,进口芯片需要进行原位替换,面对功能可裁剪的嵌入式系统,本文提出了一种基于FPGA实现的CAN总线驱动,并对其设计进行了详细介绍。

1 SJA1000

1.1 CAN通信结构

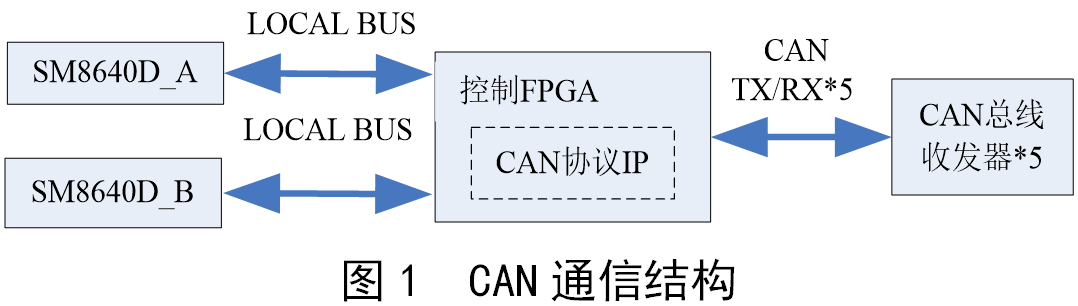

CAN通信结构如图1所示,以FPGA实现的CAN协议IP核为中心,采用CPU+FPGA+驱动器的架构。FPGA和CPU之间通过Local Bus进行通信,外挂国微SM65HVD230D型收发器对外进行CAN通信[4],模块支持5路CAN总线接口。

1.2 CAN通信帧

CAN通信帧分为两种,包括11位标识符的标准帧和29位标识符的扩展帧,两者只是在标识符长度即帧ID的长度上不一样。

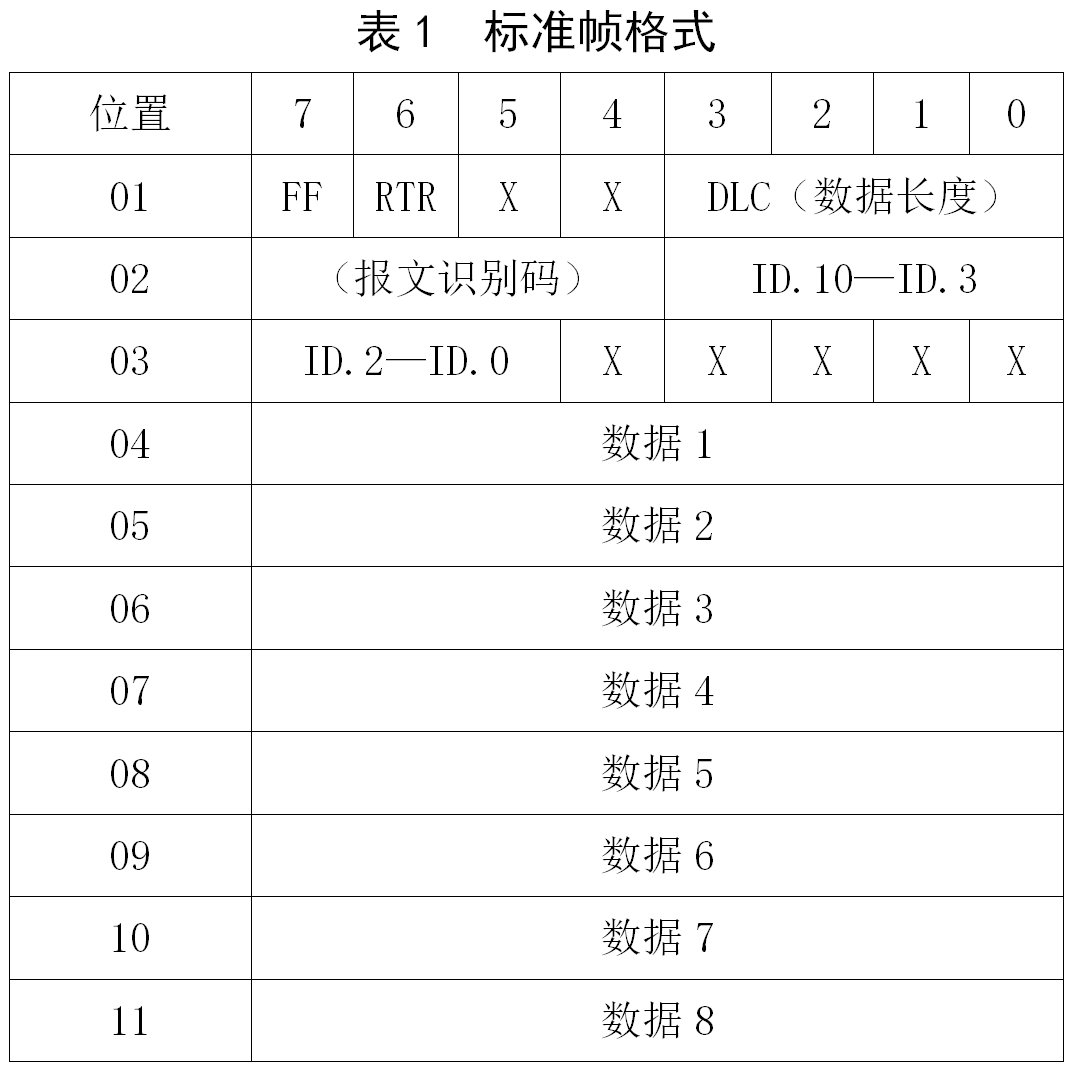

CAN标准帧信息包括信息和数据两部分共11个字节,前3个字节为信息部分,后8个字节为数据部分。第一个字节为帧信息,其中前4位DLC表示数据帧的实际长度,第6位(RTR)为帧类型,数据帧设置为0,远程帧设置为1;第7位(FF)为帧格式,标准帧设置为0。标准帧格式如表1所示。

CAN扩展帧信息为13个字节,前5个字节为信息部分,第一个字节与标准帧相同,剩余信息部分为报文识别码[5]。扩展帧格式如表2所示。

CAN协议建立在OSI7层开放互联参考模型基础之上,定义了数据链路层和物理层,保证节点间无差错传输。

2 CAN驱动实现

通过FPGA实现了SJA1000芯片功能,能够正确传输CAN通信帧;要完成数据的完整发送还需要对来自CPU的数据进行解包处理,对于来自其他模块的CAN通信帧进行组包。因此,CAN驱动的设计由五部分构成:CAN初始化、CAN通信帧发送和接收以及CAN通信帧的组包和解包。

2.1 CAN初始化

综合电子战管理系统中存在大量的CAN节点,因此采用扩展帧进行通信。CAN初始化主要完成根据扩展帧定义的数据结构的初始化以及相关寄存器的配置[6]。

CAN通信帧的帧格式设置为扩展帧,帧类型设置为数据帧,每帧的数据长度设置为8个字节,数据和报文识别码初始化为0。在通信帧发送之前需要根据用户需求对以上数据重新设置,确保通信帧的正确性。初始化还需要申请用于存放接收的通信帧ringbuffer空间,用于存放多组通信帧。对CAN寄存器的配置主要包括波特率、中断使能、时钟分频以及输出控制器等。以波特率配置为例,需要对总线时序寄存器0和总线时序寄存器1同时进行配置,两个寄存器根据约束条件能够搭配出不同的采样率以适应不同的系统需求。初始化还包括信号量创建、中间数据存储空间申请、中断挂接以及获取CAN通信帧任务的创建。

2.2 CAN通信帧发送和接收

CAN通信帧发送前完成通信帧的配置并对传输缓冲区状态进行判断,在发送结束前对传输完成状态进行判断,确保通信帧已完成发送。

CAN通信帧接收之前对接收缓冲区状态进行判断,当存在数据消息时进行获取。通信数据的全部CAN通信帧接收完成之后需要进行组包处理,因此需要先将这些CAN通信帧存储到缓冲区中。每次完成通信帧的接收通过设置命令寄存器释放接收缓冲区,确保后续通信帧的正确传输。

2.3 CAN通信帧的组包和解包

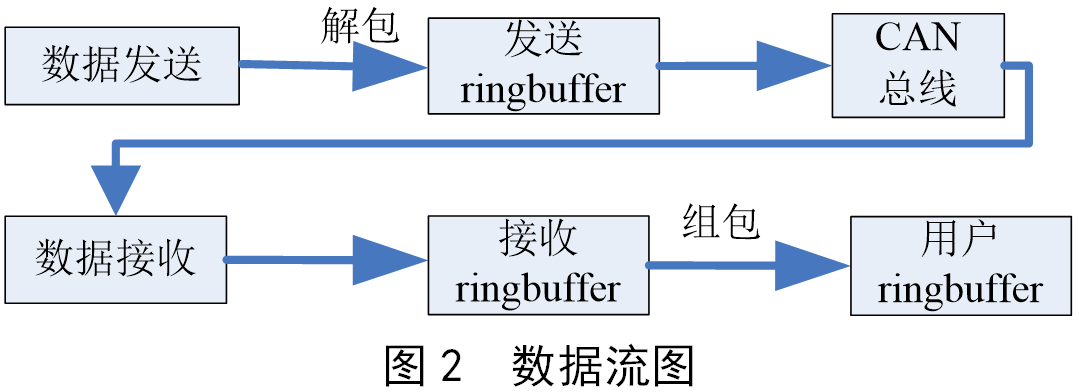

CAN通信帧的解包将来自用户的数据分解成CAN通信帧,通过调用CAN通信帧发送接口将每一帧CAN数据发送出去。CAN通信帧的组包将来自CAN总线通信帧中的数据部分进行组装拼接,将完整的数据反馈给用户。

完成用户的数据的解包,需要对每个通信帧的数据进行存储,然后统一将这些CAN通信帧发送出去。因此CAN通信帧的发送也需要建立发送ringbuffer进行临时存储,发送ringbuffer的大小不小于解包后的数据量。为保证发送ringbuffer中数据的正确性,对解包进行同步处理,即在解包前获取信号量,在发送完成后释放信号量。

CAN通信帧的发送通过写控制寄存器完成,便于控制;接收则是通过中断方式完成,效率高。

为了提高系统性能,在初始化阶段创建接收CAN通信帧的任务,接收任务的优先级大于应用任务,确保数据接收的效率。接收任务完成CAN通信帧中数据的组装和拼接,将组装完成的数据暂存到用户数据ringbuffer中,在用户发起数据获取操作时将数据反馈给用户。

CAN总线驱动设计中采用发送ringbuffer、接收ringbuffer和用户数据ringbuffer三重数据缓冲结构,使得用户发送和接收的数据的正确性、完整性得到保障。CAN通信的数据流图如图2所示。

综合电子战管理系统中CAN网络逻辑互联采用多网段独立拓扑方式,通过FPGA实现5路独立的CAN总线功能。CAN总线需要对5路进行初始化,数据的发送通过同步机制按顺序下发5个通道的数据,数据的接收则对5个通道的数据同时存储。

3 功能测试

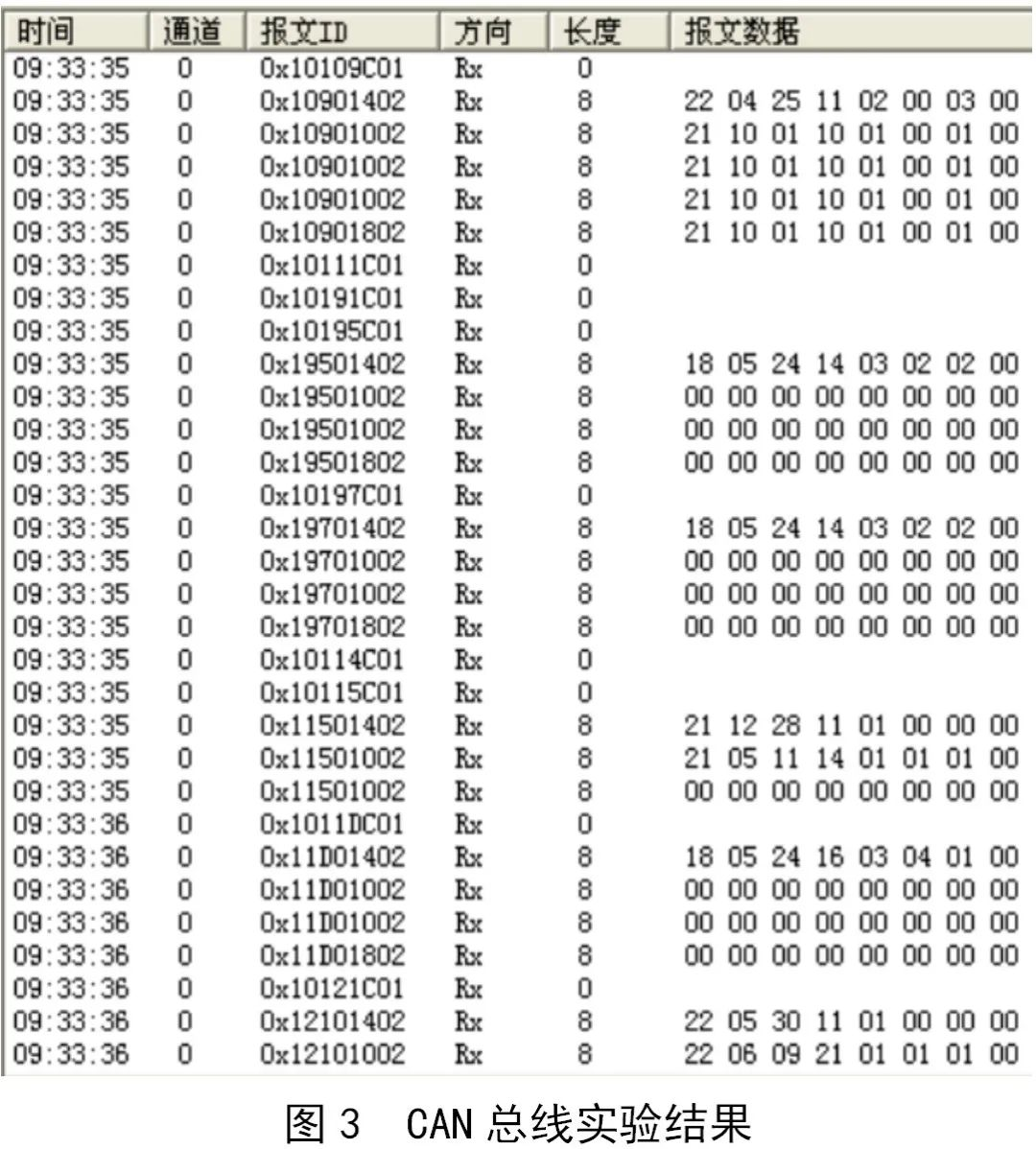

自测试阶段完成了5路CAN总线的自环测试,单通道发送,剩余通道接收。联试阶段将本文的CAN总线驱动应用于某综合电子战管理系统,计算机板为主节点,与机架内的其他模块一起挂接在CAN 0通道上,机架外4台设备分别连接到剩余4个通道。

主节点发送数据到5个通道中,通过CAN盒可以检测到CAN总线中的数据。系统初始化成功后,主节点与其他节点间进行了长时间的通信,经测试该系统稳定、可靠。CAN总线0通道实验结果如图3所示。

4 结语

本文研究了基于FPGA的CAN总线驱动设计,提出了三重环形缓冲结构,并以某综合电子战管理系统为应用背景,对该驱动设计进行了测试,验证了该驱动的正确性以及该设计的可靠性。