概述:

本文介绍Power PC处理器MPC8247与EEPROM(RTC)芯片X1226的通信在vxworks下的实现。

芯片简介:

MPC8247是一款功能丰富的通信处理器,它集成了一个高性能的PowerPC RISC微处理器,一个灵活的系统集成单元,以及许多可用于不同应用的通信外围控制器,特别是通信和网络系统。

X1226 是一个带有时钟,日历,两路报警,512 x 8位的EEPROM,振荡器补偿和电池切换的实时时钟。振荡器使用一个外部的,低价格的32.768Khz的晶体。

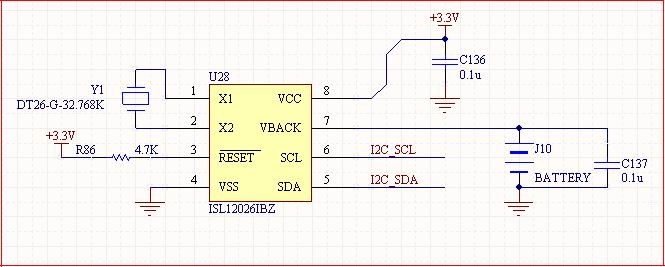

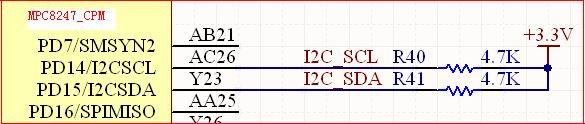

硬件电路:

1) 晶振为32.768K

2) I2C_SCL和I2C_SDA为漏极开路,接上拉电阻

原理分析:

MPC8247上有一个I2C控制器(inter-integrated circuit),通过它可以与别的I2C设备交换数据,诸如EEPROM,实时时钟RTC,A/D转换器,LCD显示器,温度传感器…

在I2C数据传输的过程中,等待状态将会在SCL保持低的时候自动插入,作为主的I2C控制器会通过检测SCL来判别是否需要等待状态。因此,不需要人为加入等待延时操作。

主要特点:

1)两个信号接口(SDA和SCL)

2)支持主和从操作

3)支持多主环境

4)连续传输模式和自动扫描外设

5)支持最大2.080KHz的时钟率

6)独立的可编程的波特率发生器

7)支持7-bit的I2C地址

8)漏极开路输出信号允许多主配置

9)本地回环测试功能

以上这些特点在I2C初始化和调试的时候都需要考虑和应用到。

I2C控制器的传输

主I2C控制器通过发送一个指定了读或写请求的消息给一个I2C从设备来初始化一次传输,第一个消息字节包含一个7-bit的从设备地址和一个R/W请求位。

如果是对从设备写,主设备会发送一个包含从设备地址和写请求(R/W=0)的字节,后跟需要写入的数据。如果是对从设备读,主设备会发送一个包含从设备地址和读请求(R/W=1)的字节。

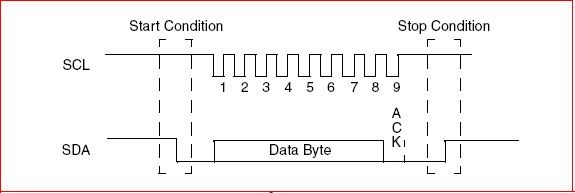

I2C的传输时序间下图:

I2C主设备的写(从设备读)

如果MPC8247是主设备,在初始化一个写操作之前,需要准备一个发送buffer和buffer 描述符。

按如下步骤进行:

- 主核心置位I2COM[STR]

- I2C主设备产生一个开始条件 – 在SCL高的时候,SDA上一个高到低的跳变,接着SCL产生脉冲,数据在SDA上移出。

- 从设备确认每个字节并写入到它的当前接受buffer,直到一个新的开始或者停止条件被检测到。

- 发出每个字节后,主设备都会监测确认条件。如果从设备没有确认某个字节,发送将会停止,主设备产生一个停止条件 – 在SCL高的时候,SDA上一个低到高的跳变。

I2C回环测试

在主模式下,MPC8247的I2C控制器支持主设备的写入请求的回环操作。主设备简单地向它自己的地址(I2ADDR中编程)发出一个写请求。接受单元会监测发送并将发送的数据读到它自己的接受buffer中。回环操作不需要特殊的寄存器编程。

I2C主设备读(从设备写)

如果MPC8247是主设备,在初始化一个读操作之前,需要准备一个大小为n+1字节的发送buffer,n是将要读的字节数。第一个字节是从设备的地址加上读请求(R/W=1)。接下来的发送字节是用来规范时序的,可以不初始化。配置合适的接受buffer和buffer描述符来接受数据。

按如下步骤进行:

- 置位主设备的I2COM[STR]来初始化读。

- 从设备在SDA和SDL上检测到一个开始条件。

- 当第一个字节一位位全部移入,从设备将接收到的数据与它的地址进行比较。如果匹配,从设备将确认这个字节并紧接着在脉冲时序下发送数据。

- 只要没有溢出错误发生,主设备会确认每个接收到的每个字节。

I2C的寄存器

I2C模式寄存器(I2MOD)

I2MOD[REVD]确定字节的bit顺序,确定先移出的是高位还是低位

I2MOD[EN]使能I2C控制器

I2C地址寄存器(I2CADD)

I2CADDR[0-6]指定作为从设备时的访问地址

I2C波特率发生寄存器(I2BRG)

I2BRG[DIV]分频系数

I2C事件和掩码寄存器(I2CER/I2CMR)

I2CER[TXE]发送错误状态位

I2CER[TXB]当buffer中的所有的字节都写入发送队列时置位

I2CER[RXB]当接收到最后个字节并关闭接受buffer描述符时置位

掩码寄存器是设置是否产生中断,所有位都复位,不产生中断

I2C命令寄存器(I2COM)

I2C[STR]开始发送,产生开始条件

I2C[M/S]主从选择位

Input/Output Port寄存器(D口的pin 14 , pin 15)

D口数据方向寄存器(PDIRD)0x10D60

0 对应的pin脚作为输入管脚或者双向的输入输出管脚

1 对应的pin脚作为输出管脚

D口pin脚分配寄存器(PPARD)0x10D64

0 通用I/O口

1 专用外围功能

D口专用选项寄存器(PSORD)0x10D68

0 专用外围功能 1

1 专用外围功能 2

D口漏极开路寄存器(PODRD)0x10D6C

0 I/O口驱动为输出

1 I/O口漏极开路

通信处理命令寄存器(0x119C0)

[0]RST 软件复位命令

[1-5]PAGE 指明分配给下一级块的parameter RAM页号

01011 I2C

[6-10]SBC 下一级块号

01010 I2C

[15]FLG 命令标志

0 CP可以接收新的命令

1 CPCR中有一个CP正在处理的命令

[28-31] 操作代码

0000 初始化接收和发送PARAMS

0001 初始化接收PARAMS

0010 初始化发送PARAMS

注:初始化值为:0x29610000

I2C Parameter RAM

I2C控制器的parameter table用于通用的I2C参数。通信处理器CP使用用户编程的指针(I2C_BASE)来对I2C parameter table进行访问。I2C_BASE(0x8AFC)在parameter RAM里。

I2C parameter table能够放在dual-port RAM里任何64字节对齐的地址。在使能I2C之前,用户必须初始化某些parameter RAM值,CP初始化其它值。

I2C parameter memory map

0x00 RBASE 半字

0x02 TBASE 半字

Rx/TxBD table 基地址,指明 BD tables从dual-port Ram的起始地址

0x04 RFCR 字节

0x05 TFCR 字节

Rx/Tx功能代码寄存器

[3-4] Byte ordering (1x Big-endian)

I2C Buffer Descriptor (BD) Table

Buffer descriptors(BDs) 在 dual-port RAM里面是独立组织的。

CP使用BDs来确认接收和发送或者指示错误条件使得处理器核心知道buffers已经被处理了。

需要说明:

I2C_BASE

某些协议,诸如SMCx,SPI,I2C,只有两个字节来存储parameter RAM。

Parameters并没有存储在这两个字节里。而是通过这两个字节来指定一个用户可编程的指针来定位parameters存储的地方。详见AN2147.pdf page 2。

接收和发送buffer descriptor报告每个发送buffer的信息,以及控制某个可屏蔽的中断是否需要产生。

offset+0开始的半字包含状态和控制位。CP在每个buffer发送或接收后会更新这些状态位。

offset+2开始的半字包含发送或接收到的数据长度(字节)。

offset+4指向buffer的起始处。

RxBD,指针必须是偶数,能够指向内部或外部的存储。

TxBD,指针可以是偶数也可是是奇数,能够存在于内部或者外部存储。

I2C接收buffer descriptor(RxBD) 初始值 0xb000

[0]E

Empty:

0 buffer已满或者由于一个错误而停止

1 buffer空或者接收正在处理中

[2]W

Wrap:

0 并不是RxBD table中的最后一个BD

1 是RxBD table中的最后一个BD,当前的buffer被处理后,CP将用RBASE指向的BD来接收数据。

[3]I

Interrupt:

0 当buffer满了后不产生中断

1 当CP填充buffer的时候I2CER[RXB]会置位

I2C发送buffer descriptor(TxBD) 初始值 0x3c00

[0]R

Ready:

0 buffer还没准备好发送。

1 buffer已经准备好发送。

[2]W

Wrap:

0 不是table中最后的BD

1 是table中最后的BD

[3]I

Interrupt:

0 buffer被处理后不产生中断

1 I2CER[TXB]或者I2CER[TXE]在buffer处理后将会置位。

[4]L

Last:

0 当前buffer不包含消息的最后字符

1 当前buffer包含消息的最后字

[5]S

Generate start condition

0 在buffer中的第一个字节发送前不会发送一个开始条件

1 在buffer中的第一个字节发送前会发送一个开始条件

[13]NAK

No acknowledge

没有ACK标志

[14]UN

Underrun

[15]CL

Collision