摘要:1394B总线以其高带宽、低延迟、高可靠特性在机载系统中应用越来越广泛。该文介绍了1394B总线协议,实现了一种智能1394B接口模块,并进行了通信测试,具有一定的参考意义。

关键词:1394B, 通信

1 概述

1394B总线网络与传统1553B总线系统相比具有高带宽、低延迟、高可靠性等方面优势,已经广泛应用于新一代战机的航电系统、飞行器管理系统和机电公共设备管理系统。

2 1394B总线概述

IEEE 1394-1995最初由Apple公司提出,由IEEE正式制定,支持100/200/400Mbps通信速率,其目的是为了简化计算机的外部连线,并且为实时数据传输提供一个高速接口[1]。2000年对IEEE 1394-1995标准进行补充,增强了互操作性,解决了一些二义性问题,形成了IEEE 1394a-2000。2002 年起,对IEEE 1394-1995 规范进行了不断地完善, 确定了IEEE-1349b-2002,其目标是用于传输多媒体数据,其带宽,传输速度,距离等都有了大幅度提高[2]。

1394B总线具有如下特点:

- 采用异步流包:异步流包是异步时间间隔内发送的等时包。异步流被用于网络上大多数的通信。

- 使用STOF同步:STOF包由每条总线上的CC按照固定的帧速率发送STOF包通知总线上所有的节点新的一帧开始。通过传输一个固定速率的STOF包实现网络的同步。

- 纵向奇偶校验(VPC):纵向奇偶校验(VPC)是作为1394物理层产生的CRC校验的一个附加校验。VPC提供物理层和软件层在进行消息传输过程中的附加数据完整性的保障。

- 通道号静态分配:因为异步流包在格式上与等时包一致,所以也由通道号来确定目标节点,总线上每个节点的通道号是由应用预先分配的,根据体系结构而定。

- 带宽预分配:每一帧开始后(STOF包),总线上每个节点的发送和接收的时间由应用根据体系结构预先分配。

- 使用匿名签署协议(ASM):匿名签署协议是为了满足嵌入式实时系统需求的上测试协议,ASM协议建立于下层协议,不需要1394消息头传输ASM特殊消息[3]。

3 模块设计

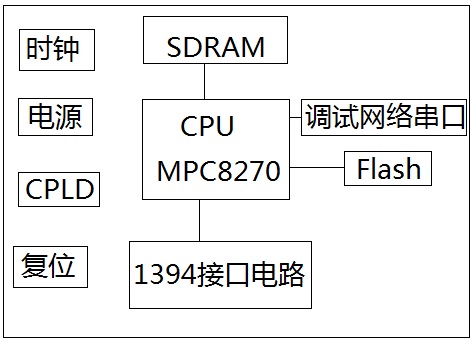

智能1394B接口采用MPC8270实现,对外提供三个1394B端口。模块主要由时钟电路,电源电路,复位电路,1394接口电路以及处理器电路组成。系统结构如图1所示。

图1 系统结构

3.1 处理器电路

处理器电路主要由处理器,SDRAM,CPLD和FLASH组成。

采用MPC8270处理器,主频266MHz,外频66MHz,提供PCI总线仲裁以及标准PCI总线接口,运行VxWorks5.5系统,完成应用数据处理以及通信传输控制和管理工作,并提供串口、以太网等调试接口。

- SDRAM:采用四片容量为512MB的SDRAM组成2GB容量的内存,工作频率66MHz,64bit宽度,作为程序和数据的存储空间。

- CPLD:CPLD固化逻辑用于实现CPU初始化配置,复位管理,片选分配等功能。

- FLASH:容量64MB,访问速度120ns,宽度32bit,用于固化Boot、OS以及应用程序。

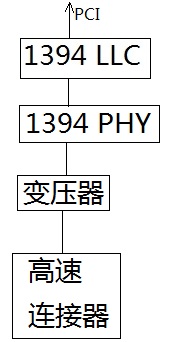

3.2 1394B接口

1394B接口属于该模块对外的应用通信数据接口,选用1394链路层和物理层实现芯片以及1394变压器,实现模块1394B接口的对外耦合。1394B电路连接示意见图2。1394链路层芯片带有独立的PCI控制器,内部带有多个DMA发送通道和接收通道。可直接挂接在主处理器的PCI接口上,通过PCI总线进行对链路层的控制。1394物理层芯片是1394B物理层芯片中的一款高性能物理层接口芯片,保持与其他物理层芯片设计的兼容性。该芯片满足OHCI、IEEE 1394-1995、IEEE 1394a-2000、IEEE 1394b-2002等协议规范;全面支持IEEE 1394b-2002协议下S100,S100β,S200,S200β,S400和S400β的传输速率;提供3个物理层端口。

图2 1394B接口电路连接示意

4 模块工作流程

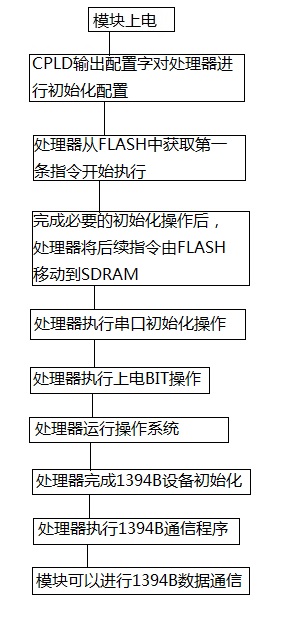

模块的工作流程如下:

- CPLD逻辑输出配置字对处理器进行初始化配置,配置的主要内容有:将CPU配置32位模式启动,内部寄存器基值为0xF0000000,启动地址为0xFFF00100,内核工作频率为200MHz, 处理器工作在PCI Host模式, PCI接口工作频率为33MHz

- CPU从0xFFF00100(FLASH地址)获取第一条指令开始执行,通过获取的指令对CPU的中断,时钟,系统总线,SDRAM和FLASH进行初始化,并将后续的固化在FLASH中的代码从FLASH搬运到SDRAM中,搬运到SDRAM的起始地址为0x0000C000

- 完成代码搬运后,处理器开始对串口进行初始化,并在执行后续代码时通过串口输出相应的打印信息

- 处理器执行上电BIT,以及后续的BOOT代码

- 处理器运行操作系统

- 处理器调用驱动程序对1394设备进行初始化,设备初始化工作包括调用设备句柄空间的初始化、设备资源的分配、信号量的初始化、中断的使能和设备工作模式的设置等过程

- 初始化完成后,处理器可进行1394B通信。发送过程:主机应用调用异步流数据包发送函数后,由驱动检查相关参数的合法性,由主机通知链路层芯片该消息数据准备好,根据数据包发送条件判断出该数据包具备发送条件后,配置异步流发送上下文,启动DMA,链路层芯片从指定的数据包地址中将数据搬移到链路层芯片的FIFO 缓冲中发送,完成异步流的发送。接收过程:设备在接收到消息之前,首先在设备的初始化时配置异步流的接收上下文,启动接收,当设备检测到数据包到达时,物理层芯片根据接收的上下文配置,将和配置的通道号匹配的异步流数据包上传链路层,链路层启动DMA 将接收到的数据直接放在指定的主机缓冲区内,然后更新接收的上下文配置,同时更新主机的缓冲区地址

工作流程图如图3所示

图3 模块工作流程图

5 测试验证

将智能1394B接口模块安装在测试工装中,经过高速1394线缆与1394B仿真分析仪连接,运行测试程序,1394B接口模块的三个端口都能和标准设备正确通信。

6 结论

本文介绍了1394B总线协议的特点,基于MPC8270实现了三端口1394B接口模块,并进行了测试验证,具有一定的应用价值。

参考文献:

- 李世平,戴凡,汪旭东.IEEE-1394系统原理与应用技术[M].2004:1-2.

- 刘莎,阴亚芳.VxWorks下1394b总线系统驱动软件设计[J].测控技术,2013(5):96-99.

- 马宁,王宣明,郑斐.飞机管理系统1394总线AS5643协议的设计与实现[J].航空计算技术,2013(6):122-124.