摘 要: 传统低速航空总线已无法满足机载座舱大屏幕显示器高速数据通信的应用需求。针对此现状,提出了一种基于MPC8548E的高速总线通信系统。该系统以MPC8548E为核心,采用PCIE总线,通过PES12T3G2交换机扩展出2个接口,连接高速航空总线模块,实现了显示器与其他机载设备的高速数据交互;采用RapidIO总线,通过TSI578交换机扩展出3个端口,将显示器内部模块组网,实现了背板总线快速通信。经验证,本通信系统具有传输数据带宽大、传输速率快等优点,完全能够满足机载座舱大屏幕显示器外部和内部数据实时通信的应用需求。

Abstract: As the requirement of high speed data communication in Cockpit large-screen display system cannot be satisfied by the traditional low speed aviation bus, a kind of communication system based on MPC8548E is presented. In the system, PCIE bus is connected with the high speed aviation bus modules through two extension interfaces from PES12T3G2 switch to realize a high speed data exchange between the display and the other systems. The modules in the display are connected through RapidIO bus with three extension ports from TSI578 switch, which guarantees the high communication performance of the display backboard bus.

The experiments are performed to validate the performance of the communication system. The system has a property of high bandwidth and high transmission speed, which satisfies the communication requirement of the Cockpit large-screen display system.

作者:张锋,常晨晨,曹峰,钟海林

显示器是飞行员获取飞机姿态导航信息、任务信息和战场态势的关键设备[1]。随着座舱显示控制系统的发展,座舱集成化程度越来越高,显示器则是向紧凑型、集成型方向发展[2],需要显示的信息量也在不断增大[3],大屏幕显示器逐渐成为机载显示器发展的主要方向。国外研究结果表明,大面积、高分辨率的大屏幕显示器图像能显著提升飞行员的反应时间[4],显示器图像信息显示速度对飞行员实时判断和决策起着至关重要的作用。制约图像信息显示速度的主要因素是图形显示系统处理能力以及通信系统数据处理传输能力。目前国内机载显示器图形显示系统普遍采用专用图形处理芯片,处理能力大幅度提升,完全能够满足图形实时绘制要求。然而通信系统仍采用如HB6096、Arinc429等传统低速总线接口,已成为制约信息显示速度的关键因素。一方面,大屏幕显示器显示内容非常丰富,与其他机载设备交互的数据量大幅度增加;另一方面,大量航空总线数据需要在显示器内部实时传递,对通信总线的带宽和传输速度的要求不断提高。显然,机载显示器需要更高速的通信系统来满足这些需求。

MPC8548E是美国飞思卡尔公司推出的第三代PowerPC处理器,具有PCIE和RapidIO两种高速串行总线接口[5]。其中PCIE总线接口主要用于挂接高速通信模块,随着计算机和应用系统接口速率的提升,PCIE越来越明显地体现出其在高速数据采集和传输系统中应用的优越性[6]。接口支持x1、x4、x8等模式,通信带宽分别可达2.5 Gb/s、10 Gb/s、20 Gb/s。RapidIO总线接口主要用于背板总线的高速数据通信,在工业领域有着广泛的应用。接口支持x1和x4模式,通信带宽分别可达3.125 Gb/s和12.5 Gb/s。

本文提出一种基于MPC8548E的机载显示器通信系统,使用MPC8548E内部集成的PCIE和RapidIO总线接口,分别通过相应的交换机进行多端口扩展,实现显示器外部数据高速通信和内部模块间高速组网互联,可以满足大屏幕一体化显示器高实时性通信的需求。

1 系统设计

机载显示器通信系统是一种实时嵌入式系统,需要快速响应外界的突发事件,且响应时间是确定的、可预测的[7]。所以系统设计上核心处理器选用高性能高可靠性的MPC8548E,操作系统选用高可靠性、高实时性的VxWorks6.6。

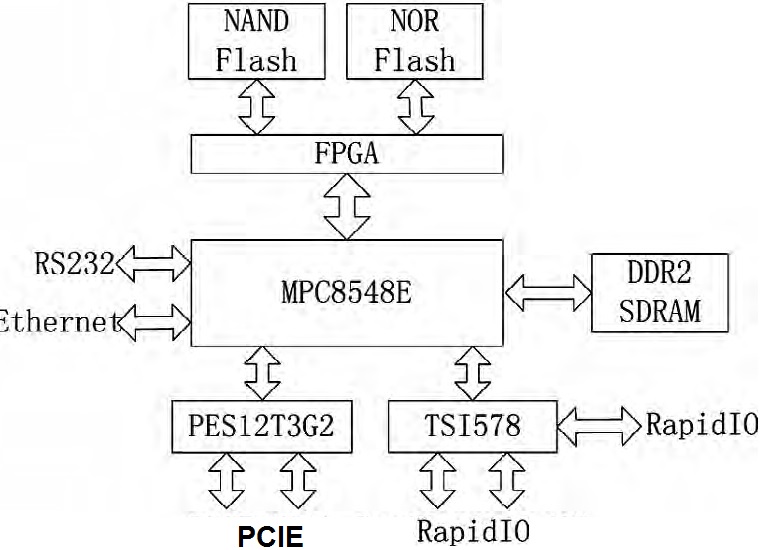

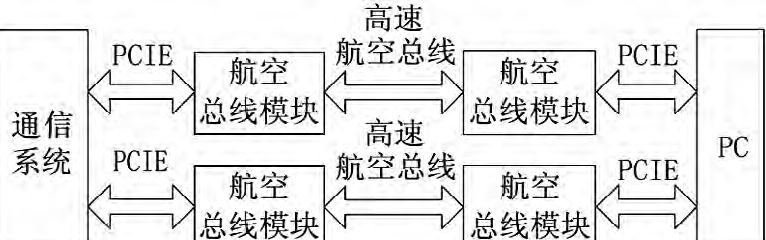

通信系统核心处理器工作主频为1.333 GHz,外接DDR2 SDRAM内存为512 MB。PCIE控制器通过交换机扩展成2路x4接口,连接外部高速通信模块,作为通信系统的航空总线接口;RapidIO控制器通过交换机扩展成3路x4端口,作为连接显示器内部其他模块的背板总线接口。系统设计采用1路RS232串口及1路千兆以太网作为软件调试接口,采用8 MB NOR Flash存储系统固件软件及VxWorks操作系统软件、256 MB NAND Flash存储通信应用软件。NOR Flash和NAND Flash通过FPGA连接到MPC8548E。通信系统结构框图如图1所示。

图1 通信系统结构框图

2 硬件扩展接口设计

2.1 PCIE总线扩展

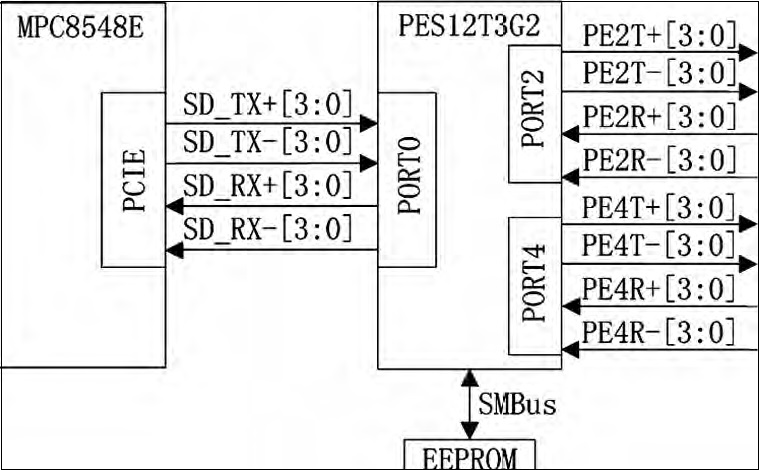

MPC8548E共有8路SerDes(串联/解串器)接口,为PCIE控制器与RapidIO控制器复用[5]。SerDes[3:0]设计用作PCIE总线的扩展接口,与交换机PES12T3G2的上行端口相连,扩展出2路下行PCIE总线接口。PES12T3G2是美国IDT公司的一款PCIE交换机芯片,具有1路x4上行端口和2路下行x4端口,支持Gen2[8]。该交换机属于透明桥类型的设备,上行/下行端口不可更改,上行端口固定在Port0,两路下行端口固定在Port2和Port4。MPC8548E兼容PCIE 1.0a协议,默认速率为2.5 Gb/s;PES12T3G2兼容PCIE 2.0协议,默认速率为5 Gb/s。在初始配置上,MPC8548E与PES12T3G2无法建立连接,所以PES12T3G2设计上需要使用外部EEPROM。PES12T3G2与EEPROM通过SMBus连接,PES12T3G2上电复位后,通过SMBus加载EEPROM中的数据进行初始化。如果处理器PCIE的默认速率与PES12T3G2相同,则PES12T3G2的初始化可以通过PCIE总线命令进行,硬件设计上减少EEPROM的使用。本设计的PCIE总线的扩展接口示意如图2所示。

图2 PCIE总线扩展

MPC8548E与交换机PES12T3G2的连接为x4模式,理论上通信系统与其他加载设备通信总速度可达10 Gb/s,有效数据载荷接近8 Gb/s。

2.2 RapidIO总线扩展

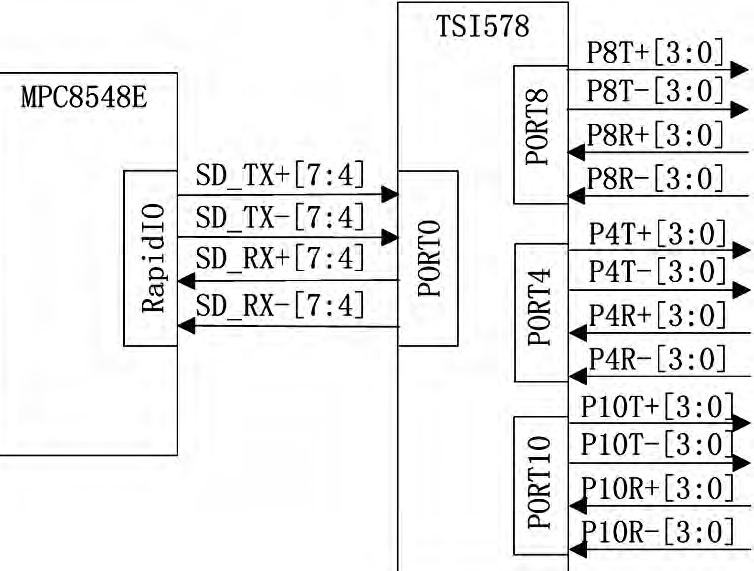

采用交换机TSI578扩展RapidIO总线的接口,实现显示器内部单元模块的组网。TSI578是美国IDT公司的第三代RapidIO交换机芯片,共有16路RapidIO端口,可配置成x1模式或x4模式,x1模式可配置16个RapidIO端口,x4模式可配置8个RapidIO端口,端口速率最大支持3.125 Gb/s[9]。TSI578的各个端口的功能相同,硬件设计配置8个x4模式的端口,其中Port0与SerDes[7:4]相连,Port4、Port8、Port12作为连接显示器内部其他单元模块的接口。MPC8548E兼容RapidIO1.2协议,TSI578兼容RapidIO1.3协议,均支持1.25 Gb/s、2.5 Gb/s、3.125 Gb/s速率,且速率可以通过硬件管脚配置,软件完成所有TSI578的初始化,无需额外EEPROM支持。本设计的RapidIO总线的扩展接口示意如图3所示。

图3 RapidIO总线扩展

配置硬件管脚,将不使用的TSI578端口关闭,以降低通信系统功耗。硬件配置MPC8548E与交换机TSI578的速率为3.125 Gb/s,理论上通信系统与显示器内部单元模块通信总速度可达12.5 Gb/s,有效数据载荷接近10 Gb/s。在显示器内部数据传递可以满足实时性要求的情况下,可以降低通信速率,进一步降低功耗。

3 软件设计

通信系统的软件包括固件软件、VxWorks操作系统软件、PCIE驱动软件、RapidIO驱动软件和应用软件。固件软件和VxWorks操作系统软件保证了通信系统的快速启动和实时、可靠的通信;PCIE驱动软件和RapidIO驱动软件提供了通信系统外部/内部通信的能力;应用软件与实际的应用需求相关。本文仅讨论PCIE驱动软件和RapidIO驱动软件相关的设计。

3.1 PCIE驱动软件

PCIE驱动软件包括两部分:一部分是交换机PES12-T3G2的初始化;另一部分是VxWorks PCIE总线初始化。

前面提到了,交换机PES12T3G2的初始化通过读取EEPROM中的数据完成,即加载相应数据完成功能寄存器的初始化。经过分析,PES12T3G2的EEPROM烧片文件主要由寄存器偏移地址及相应配置值组成,偏移地址使用2 B,配置值使用4 B,偏移地址后紧跟着对应寄存器的配置值,烧片文件的结尾包含2 B的校验。

上行端口Port0的偏移基址为0x0,寄存器空间大小0x1000;下行端口Port2的偏移基址为0x2000,寄存器空间大小0x1000;下行端口Port4的偏移基址为0x4000,寄存器空间大小为0x1000。交换机控制类的寄存器位于上行端口寄存器空间中,其他寄存器上行端口与下行端口类似。本驱动软件需要分别配置3个端口的寄存器PCICMD,偏移地址0x04,值为0x0007,打开I/O访问使能、内存访问使能、总线仲裁使能和INTx中断使能;配置寄存器PCIELCTL2,偏移地址0x70,值为0x0001,设置链接速率为2.5 Gb/s。另外配置上行端口交换机控制寄存器SWCTL,偏移地址0x404,值为0x00002008,解除交换机的寄存器锁定。最后加上数据校验,形成烧片数据文件,烧片数据文件通过烧录机固化到EEPROM中。

除了交换机PES12T3G2自身的初始化之外,VxWorks操作系统还需要初始化PCIE总线域,PCIE扩展接口才可用。分配VxWorks PCIE总线域空间,包括了两个下行端口总的PCIE空间,驱动软件设置基址0x80000000,大小为256 MB,类型为MemIO,通过修改BSP完成;根据VxWorks对PCIE总线的枚举策略,包含两个PCIE设备的总线枚举结果如表1所示。

| 总线号 | 设备号 | 设备 | PCIE 域空间 |

|---|---|---|---|

| 0 | 0 | Port0 | 不占 |

| 1 | 2 | Port2 | 不占 |

| 1 | 4 | Port4 | 不占 |

| 2 | 2 | 设备1 | 占 |

| 3 | 4 | 设备2 | 占 |

由表1可以看出,VxWorks中的PCIE总线数达到4级,超过了BSP中预设的限定值3,修改此限定值为10。

3.2 RapidIO驱动软件

RapidIO驱动软件主要实现RapidIO主端网络枚举、主从端及从端间的数据通信,提供应用软件API接口。

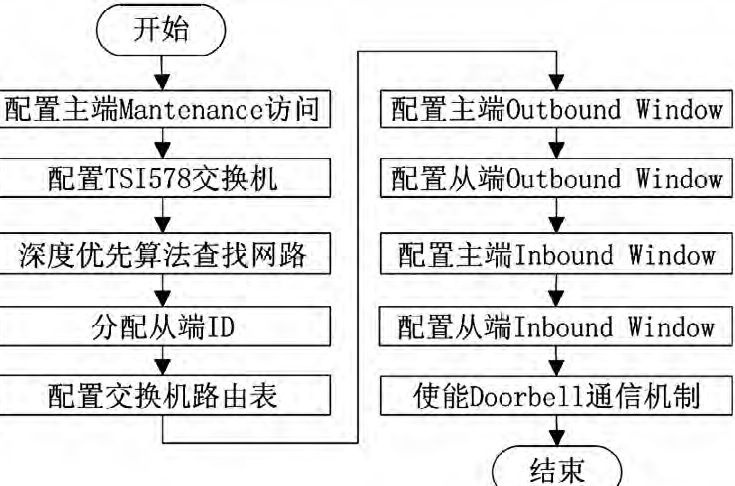

RapidIO网络枚举采用基于端口升序的深度优先算法,发现RapidIO网络中的端口个数与各端口之间的连接关系,分配每个端口一个唯一的ID,配置交换机TSI578的路由表。网络枚举过程中,主端对从端或交换机的访问通过Mantenance包完成,以跳数来区分从端或交换机。一旦发现从端设备,则锁定从端设备,分配ID,并更新主端与从端链路中的所有TSI578路由表信息。在交换机TSI578所有端口都枚举之后,根据从端设备数量,配置主端/从端相应的Outbound Window、Inbound Window寄存器,实现各主从端、各从端之间的Nwirte、Nread访问功能。最后配置数据通信中断Doorbell。RapidIO网路枚举流程如图4所示。

图4 RapidIO网络枚举流程

需要注意的是,作为RapidIO从端,使用的数据存储映射空间应不在VxWorks操作系统管理的存储空间之内,否则有可能引起操作系统异常。

4 测试验证

4.1 PCIE总线扩展验证

通信系统PCIE总线扩展接口连接2块高速航空总线模块,分别与上位机的2块高速航空总线模块进行通信和测试验证,如图5所示。

图5 PCIE总线扩展测试示意图

2块高速航空总线模块为x4模式,工作速率为10 Gb/s,在PCIE总线域中的总线号分别是2和3,其初始化、发送、接收及中断响应功能测试正常。分别在2块高速航空总线模块的发送和接收函数中添加时间测量模块,以某型显示器接收的典型数据块大小为例,分别测试PCIE总线数据写入和读取时间,测试结果如表2所示。

| 模块号 | 总线号 | 数据大小/MB | 写入时间/ms | 读取时间/ms |

|---|---|---|---|---|

| 1 | 2 | 1 | 6.6 | 9.0 |

| 1 | 2 | 2 | 13.1 | 17.8 |

| 1 | 2 | 4 | 26.1 | 35.5 |

| 2 | 3 | 1 | 6.6 | 9.0 |

| 2 | 3 | 2 | 13.1 | 17.8 |

| 2 | 3 | 4 | 26.1 | 35.5 |

从测试结果可以看出,实际数据的传输速度与理论PCIE总线的传输速度有较大的差距,原因在于高速航空总线模块的传输速率低于PCIE总线,不能完全发挥PCIE总线性能。

4.2 RapidIO总线扩展验证

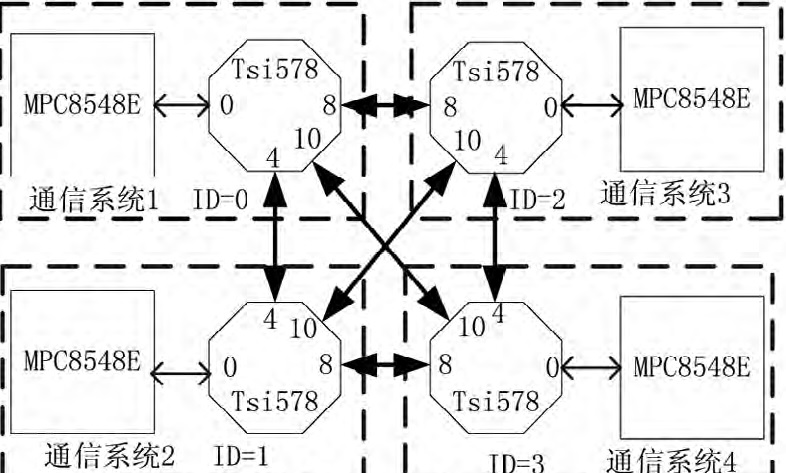

4块通信系统模块通过交换机TSI578组网互联,对RapidIO总线接口进行测试验证,如图6所示。

图6 RapidIO总线接口测试示意图

通信系统1为RapidIO网络主端,ID为0,其余端口为从端。主从端及各从端之间的Nwrite和Nread访问功能测试正常,主从端Doorbell中断响应正常。在x4模式,工作速率为12.5 Gb/s,主端映射窗口为4 MB的条件下,以某型显示器内部传递的典型数据块大小为例,测试主端与3个从端之间的数据访问时间,测试结果如表3所示。

| 主端 | 从端 | 数据大小/MB | Nwrite 时间/ms | Nread 时间/ms |

|---|---|---|---|---|

| 0 | 1 | 1 | 3.1 | 4.7 |

| 0 | 1 | 2 | 5.6 | 9.3 |

| 0 | 1 | 4 | 11.2 | 18.5 |

| 0 | 2 | 1 | 3.2 | 4.8 |

| 0 | 2 | 2 | 5.7 | 9.5 |

| 0 | 2 | 4 | 11.4 | 18.9 |

| 0 | 3 | 1 | 3.2 | 4.8 |

| 0 | 3 | 2 | 5.7 | 9.5 |

| 0 | 3 | 4 | 11.4 | 18.9 |

从测试结果可以看出,Nwrite速率在350 MB/s左右,Nread速率在200 MB/s左右。在实际使用过程中,显示器内部数据传递主要使用Nwrite,显示器内部数据传递效率高于显示器外部数据接收效率。

本文针对机载显示器实时通信受制于低速总线的问题,采用交换机PES12T3G2和 TSI578设计了基于MPC8548E的机载显示器通信系统。通过扩展,显示器外部可以连接两路高速航空总线模块,内部可以将各模块互联,实现了机载显示器的高速、实时通信。经过测试发现,显示器可以在规定周期内完成4 MB数据块的航空总线数据交互和显示器内部数据传递。实际上,高速航空总线模块并不能完全发挥通信系统的高速通信性能,机载显示器通信系统完全可以满足当前航电通信需求。随着航电系统技术以及大屏幕一体化显示器的快速发展,本通信系统有着广阔的应用空间。

参考文献

- [1] 熊华刚,王中华.先进航空电子综合技术[M].北京:国防工业出版社,2009.

- [2] 张焕春.飞机座舱综合图形显示系统关键技术研究[D].南京:南京航空航天大学,2003.

- [3] 单寅.基于VxWorks的机载图形显示系统软件研制[D].南京:南京航空航天大学,2012.

- [4] 王旭峰.机载大屏幕显示器人机工效及其标准初探[J]. 航空科学技术,2013(3):29-30.

- [5] Freescale.MPC8548E PowerQUICC III integrated host processor family reference manual[Z].2005.

- [6] 王晓庆,周晓波,赵强.PCIE高速数据采集系统的驱动 及上位机软件开发[J].计算机应用与软件,2013,30(9):331-333.

- [7] 杜文风,王博文.基于嵌入式的实时通信协议栈研究与设计[J].电子技术应用,2013,39(2):26-28.

- [8] IDT.89HPES12T3G2 PCIE switch preliminary user manual[Z].2010.

- [9] IDT.Tsi578 serial RapidIO switch user manual[Z].2010.