- 说明

- 点击数:1157

当系统架构师坐下来设计他们的下一个平台时,他们首先会查看 CPU、加速器、内存、闪存、网络接口卡以及 PCI-Express 控制器和交换机供应商提供的一系列路线图。在混合计算和内存类型的系统设计以及共享加速器和内存等组件的集群中,交换机变得越来越重要。

- 说明

- 点击数:1401

1、应用层

应用层是TCP/IP协议的第一层,是直接为应用进程提供服务的。(数据单元:报文),支持万维网的http、支持电子邮件的smtp、支持文件传送的FTP协议。

- 说明

- 点击数:5933

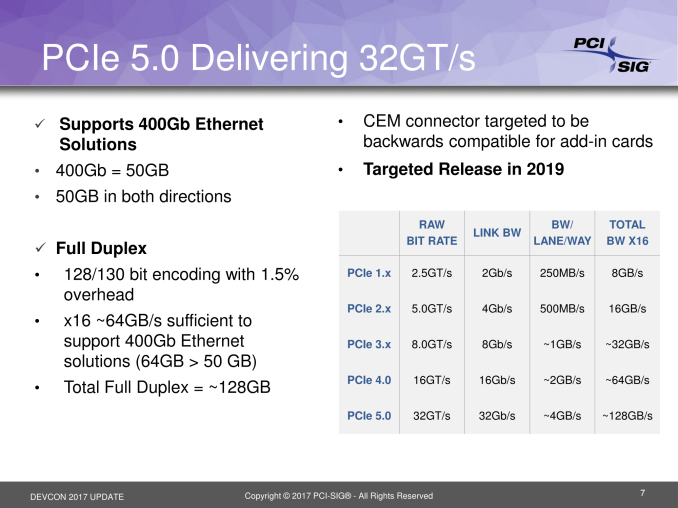

PCIe总线是服务器系统里最重要的总线,经过PCIe信号的互联,CPU得以与各种外设部件进行通信。在这些年,追赶业界带宽需求的PCIE和PCIe 6.0规范及之后的技术展望等文章里,我们即回顾了PCIe信号发展的历史,又重点探讨了最前沿的PCIe 6.0规范的性能指标。PCIe 6.0 Base Specification目前刚刚发布Draft 0.5版本,预计要到2021年才会正式发布;PCIe 6.0 CEM Specification的制定还未启动,PCI-SIG组织正在酝酿之中。与此同时,随着Intel支持PCIe 4.0的Ice Lake Xeon-SP CPU即将在今年底发布,再加上支持PCIe 4.0的AMD EPYC CPU和一众ARM CPU的逐渐出货,PCIe 4.0即将在2021年成为市场上的主流。在当下这个时间节点,广大服务器设计人员可能更应该关注会在2021-2022之间成为谈论热点的PCIe 5.0。

PCIe 5.0的主要特性

PCIe 5.0 Base Specification已经在2019年5月正式发布,但与之配套的定义Add-in-Card设计和性能要求的PCIe 5.0 CEM Specification刚刚公布Draft 0.7版本,定义电气信号测试方法的PCI Express 5.0 Architecture PHY Test Specification还未开始制定。因此,PCIe 5.0当前的重点已经从信号设计转向了信号测试方法的制定。

- 说明

- 点击数:1676

本文分享电子系统中信号波形的动图,有助于帮助我们理解传输的机理。

1. SPI传输

图1 SPI 数据传输

- 说明

- 点击数:3308

长期以来,SATA、SAS盘统治着企业级存储,虽然前些年 SSD固态存储介质的出现对 AHCI协议类型的存储访问带来了一定性能提升,但与 CPU 的计算速度相比,只能是杯水车薪,并且 SSD 的性能也不能充分地得到发挥。传统存储技术也由于访问路径长、时延大和吞吐量低而越发不能满足 “大数据” 存储的需求,并且饱受诟病。

近几年推出的 NVMe 技术以 PCIe作为 SSD 的访问接口,极大地缩短了 I/O 的访问路径,同时 NVMe 的软件栈也以精简的调用关系进一步降低了数据访问的时延。可以说,NVMe 技术的出现和快速发展,是对存储技术领域的重大革新。由此 NVMe 存储的应用自然成了业内的发展趋势,各厂商也都积极投入NVMe存储的研发中来。

越来越多的分布式文件系统积极参与全闪阵营,通过横向扩展能力,对外提供块、对象、文件服务接口及一些增值特性服务,可以通过存储节点堆叠,获得容量和性能的同步提升。硬件上使用 RDMA、NVMe、NVDIMM等先进技术,提供高性能的硬件节点;同时采用软硬件一体化的设计达成高可靠性的目标。为了减少存储产品面临的传统共性问题,如频繁的系统调用和上下文切换、多次的数据拷贝、过高的协议栈开销、复杂的并发互斥等痛点问题,在用户态化实现的过程中,引入了 Intel 的 DPDK/SPDK作为关键基础技术来进行集成和开发。基于 DPDK 和 SPDK 的用户态实现前端NVMe-oF、FCP、iSCSI 块服务相关接口。

DPDK/SPDK 技术的引入,通过大页(Huge page)、轮询、分核、无锁化等机制减少了 CPU 上下文切换、并发互斥等带来的系统开销,提高了 I/O 的响应速度,带来了系统性能的提升,有效地解决了前端网络、后端网络和落盘等环节存在的性能瓶颈。同时 SPDK 提供的 BDEV 框架,定义了上层的访问接口,和下层存储设备的注册接口,向上可以支撑多种不同协议的Target,向下可以挂载多种不同的存储设备。BDEV 框架实现了对后端存储设备的统一抽象,可以和后端存储解耦,产品前后端可针对框架开发,减小模块耦合,进行独立的测试验证,提高了产品开发维护的效率。

Intel DPDK/SPDK 技术作为该产品设计的关键一环,与分布式架构融合应用,充分发挥全闪(NVMe)存储设备和 RDMA 传输通道的能力,提供了高性能的系统特性。当前产品开发的先期任务主要完成针对新技术的可行性分析、验证及高性能硬件节点的原型机开发:兼容业界主流厂商的 RDMA、FC卡,并基于 DPDK/SPDK 实现前端 NVMe-oF、FCP、iSCSI 块服务类型接口。当前的开发实现,验证了新一代全闪(NVMe)技术的高性能能力,为最终的分布式全闪(NVMe)存储产品的实现打下了坚实的基础。

© 2026 VxWorks Club