在高性能计算和存储应用中,DDR3内存接口是FPGA设计中不可或缺的一部分。

Xilinx FPGA提供了一种MIG(Memory Interface Generator)的IP核,用于简化DDR3的设计。

本文将详细介绍Xilinx FPGA平台上的MIG IP核,包括MIG结构、读写时序等。

一、MIG IP核介绍

MIG是Xilinx FPGA中一个功能强大的内存接口IP,通过图形化配置流程可以自动生成DDR3控制器,从而简化了DDR3内存的设计。

通过使用MIG,FPGA开发者可以专注于实现应用逻辑,而无需担心底层的硬件接口细节。

MIG的主要优点是它可以大大减少设计时间,因为它自动处理了许多复杂的设计任务,如电源管理、信号完整性分析和时序控制。

二、MIG IP核接口

1、MIG IP结构图

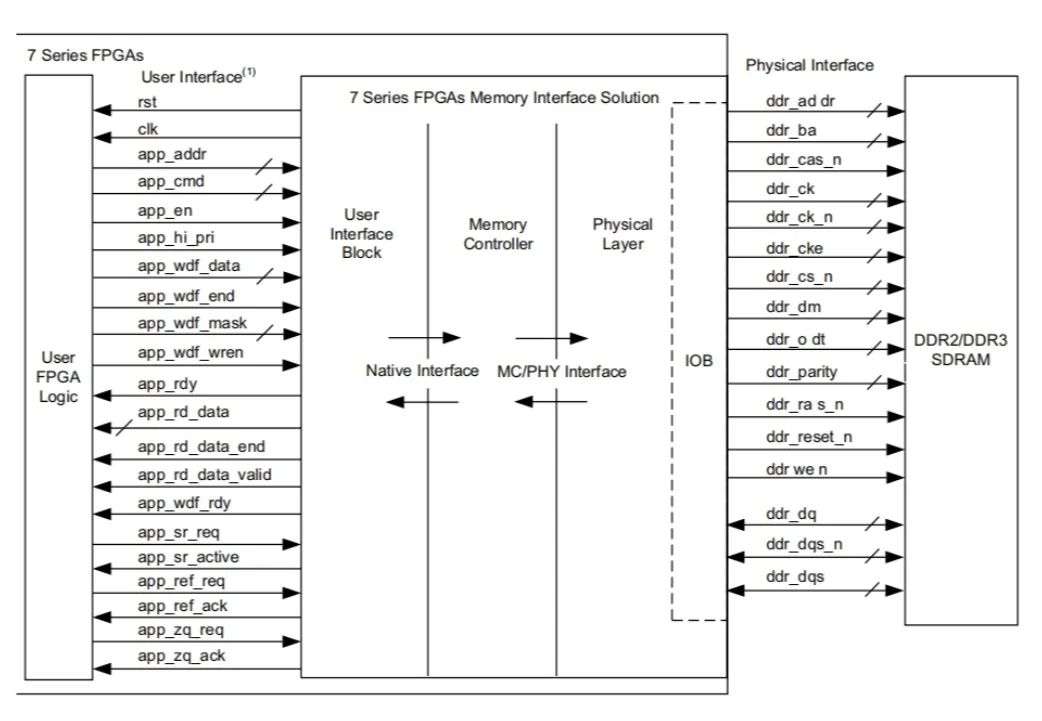

MIG IP 主要结构如下图所示,由 User Interface Block, Memory Controller 和 Physical Layer三部分组成。

这个IP 最底层是连接 DDR3 的物理接口(Physical Interface),最上层是用户逻辑控制接口(User FPGA Logic)。

我们控制ddr3的读写,主要是控制UI端的各个接口信号,这需要完全掌握mig的读写时序。

2、用户UI接口

(1)app_addr

表示当前正在提交给用户界面的请求的地址。 这里包含了整个DDR SDRAM 的所有地址字段。

(2)app_cmd

读写控制命令,读数据用001表示,写数据用000表示。

(3)app_en

表示当前命令是否有效,与app_addr ,app_cmd 和 app_hi_pri等信号同步,告诉UI当前命令有效。

(4)app_hi_pri

表示当前请求是高优先级。

(5)app_wdf_data

表示写入ddr的数据。

(6)app_wdf_end

表示当前写入突发的最后一个数据标志位,与app_wdf_wren保持一致即可。

(7)app_wdf_wren

表示 app_wdf_data 总线上的数据有效。

(8)app_rd_data

表示从ddr中读取出来数据。

(9)app_rd_data_end

表示当前读取突发的最后一个数据标志位。

(10)app_rd_data_valid

表示app_rd_data 总线上读取出来的数据有效。

(11)app_rdy

表示当前UI中的状态,1表示已准备好接受请求,0表示UI正忙。

(12)app_wdf_rdy

表示UI中写入数据fifo是否准备好接收数据,1表示fifo未满,0表示写入fifo已满。

(13)app_wdf_mask

表示app_wdf_data 的哪些位被写入外部存储器,哪些位保持不变。

(14)ui_clk和ui_clk_sync_rst

UI 输出时钟和复位信号。

(15)init_calib_complete

表示ddr是否校准完成。

三、MIG读写时序

1、读写命令与地址

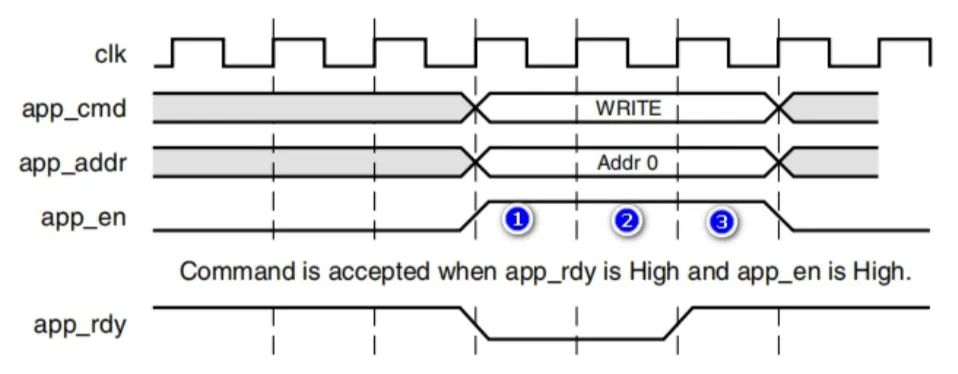

上图中时序图,只有③时刻 app_en 和 app_rdy 同时为高电平,输入的 app_cmd(命令)和app_addr(地址)才有效。

app_rdy信号为高电平时表示MIG UI处于空闲状态可以接收命令和地址,这时将app_en拉高,输入的读写命令和地址才会传入MIG UI。

2、写数据时序

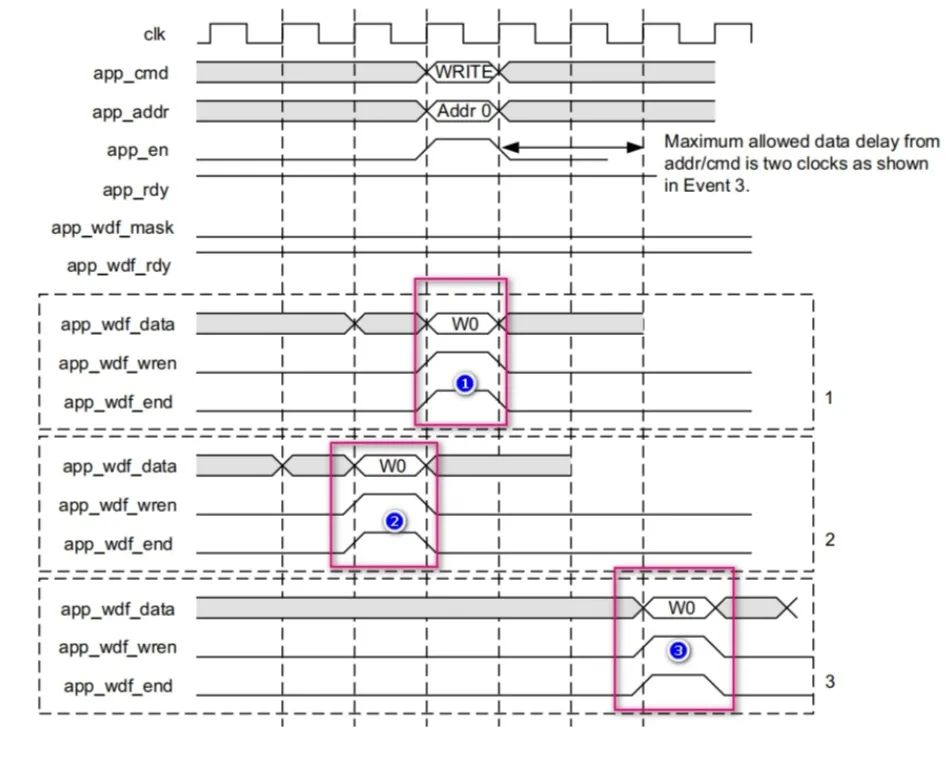

写数据时序如上图,主要是“写控制命令(app_cmd,app_addr,app_rdy,app_en)”与“写数据命令(app_wdf_rdy, app_wdf_wren, app_wdf_end,app_wdf_data )”前后的关系,有三种写数据逻辑可选。

- 表示写操作命令与写数据命令同时有效。

- 表示写操作命令比写数据命令要晚几个周期,这里就是先将数据先写入MIG中的输入数据fifo,再发送写地址和写命令。

- 表示写操作命令比写数据命令要早几个周期,最多两个用户时钟周期。

这里需要注意的是写数据命令,当app_wdf_rdy为高电平时,表示输入数据fifo未满,可写入数据。

3、读数据时序

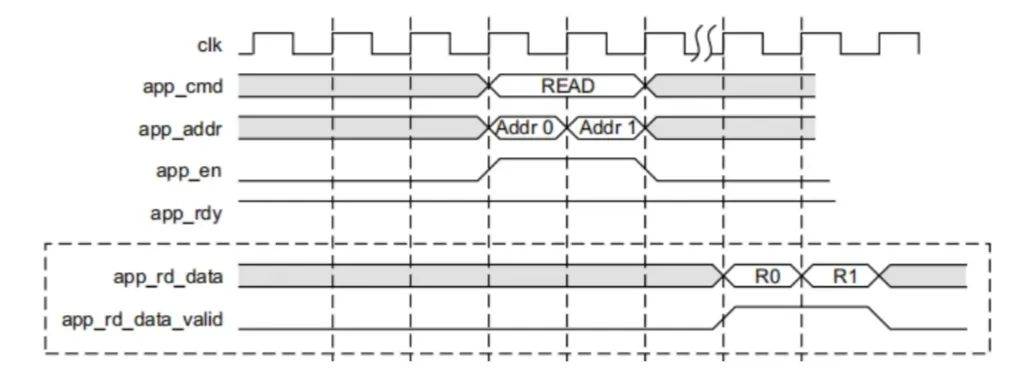

读数据时序如上图,主要包括“读控制命令(app_cmd,app_addr,app_rdy,app_en)”与“读数据通道(app_rd_data_valid, app_rd_data)”。

读数据时序很简单,当app_rdy为高电平,发送读地址和读命令后,即可等待接收数据即可。