DDR4内存的初始化过程是确保内存模块能够高效、稳定运行的关键步骤。这个过程主要包括以下四个阶段:

- Power-up and Initialization

- ZQ Calibration

- Vref DQ Calibration

- Read/Write Training (a.k.a Memory Training or Initial Calibration)

1. Power-up and initialization

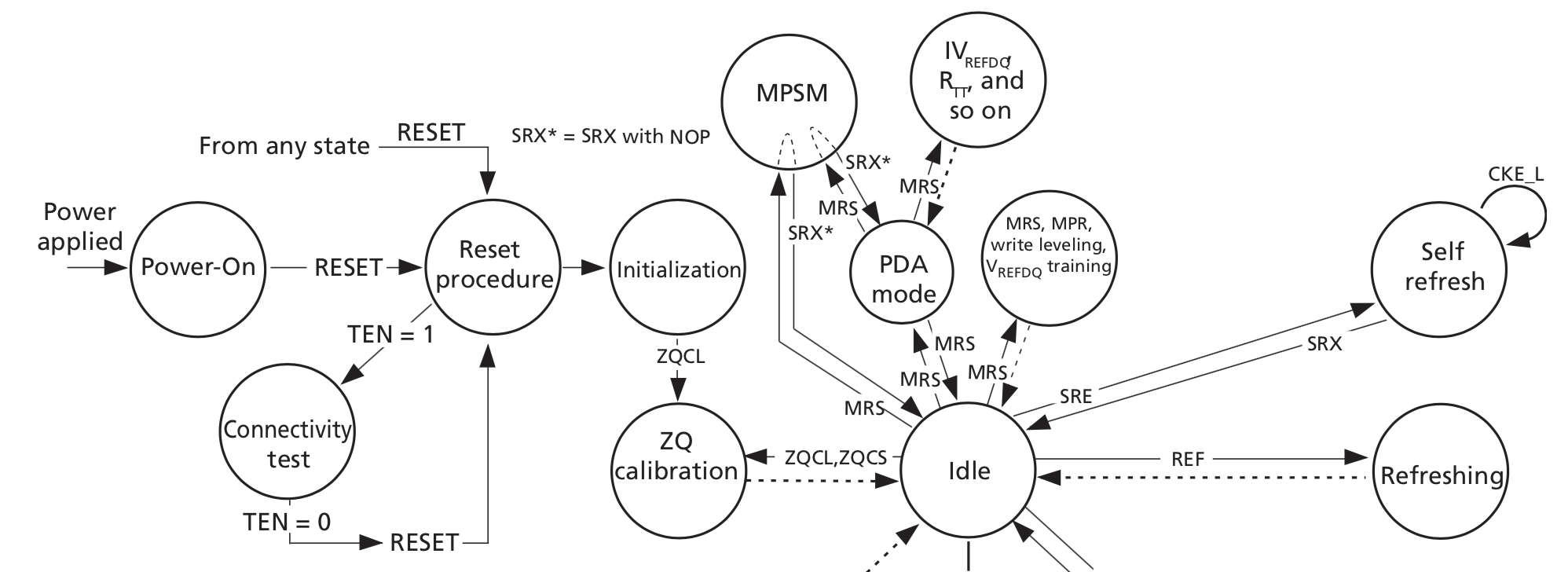

上电与初始化是由一系列精心设计的步骤组成的序列(sequence)。一般来说,在系统上电之后,ASIC/FPGA/处理器中的 DDR 控制器会被从复位状态中释放,自动执行上电与初始化序列。

- Apply power to the DRAM

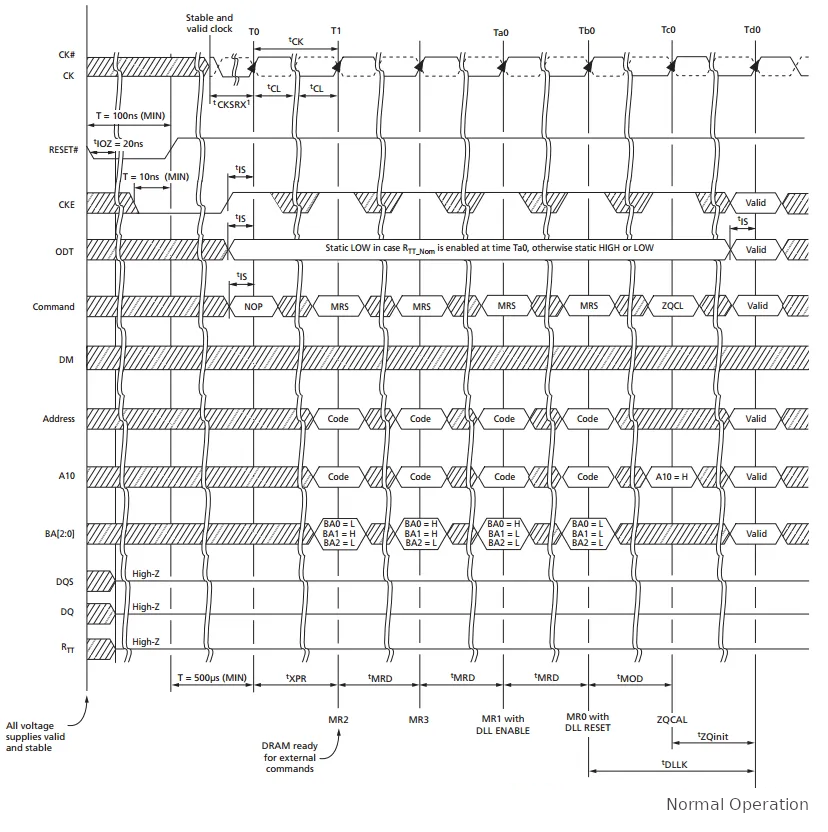

- De-assert RESET and activate ClockEnable CKE

- Enable clocks CK_t/CK_c

- Issue MRS commands and load the Mode Registers [The mode registers are loaded in a specific sequence]

- Perform ZQ Calibration [ZQCL]

- Bring the DRAM into IDLE state

2. ZQ Calibration

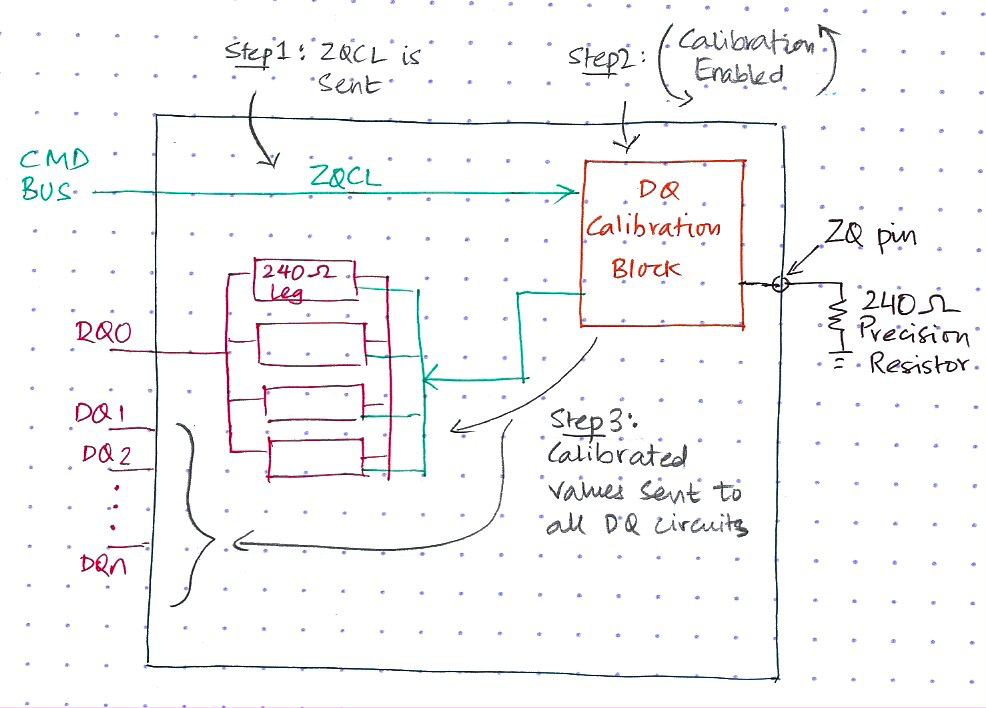

在DDR内存的初始化过程中,ZQ校准是一个重要的步骤,它确保了内存模块的信号完整性和稳定性。ZQ校准主要分为两种命令:ZQ Calibration Long(ZQCL)和ZQ Calibration Short(ZQCS)。

ZQ Calibration Long (ZQCL):

ZQCL命令通常用于系统上电初始化或设备处于复位状态时。它解决了制造工艺变化的问题,并将DRAM校准到初始温度和电压设置。

上电初始化后,第一次使用ZQCL命令的完全校准需要512个时钟周期才能完成。在此校准时间内,内存数据总线必须保持完全空闲和安静。

在初始校准之后,DRAM空闲的任何时候,都可以发出后续的ZQCL命令。对于这些后续命令(在初始化和复位以外的时间发出的命令),完成校准所需的时间窗口减少到256个时钟周期。

ZQ Calibration Short (ZQCS):

ZQCS命令用于正常操作期间的周期性校准,以跟踪连续的电压和温度变化。周期性短校准使DRAM能够在整个电压和温度范围内保持线性输出驱动器和端接阻抗。

ZQCS命令需要64个时钟周期才能完成。

DDR4有一组并联的 240Ω 电阻器可以让您调整驱动强度(用于 READ)和终端电阻(用于 WRITE)。每个PCB布局都是不同的,所以需要这种调整能力来改善信号的完整性,最大限度地提高信号的视距,并允许DRR4高速运行。

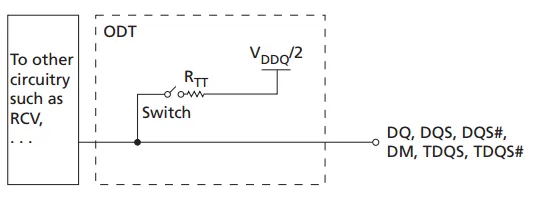

RTT_NOM:

RTT_NOM是正常操作时的终端电阻值。当内存的ODT引脚被激活时,DRR会使用这个电阻值来终结信号,以减少信号反射和提高信号完整性。RTT_NOM的值可以在模式寄存器中设置,并且在不同的操作条件下可能会有所不同。

RTT_WR:

RTT_WR是写操作时的终端电阻值。当内存接收到写命令时,不论ODT pin的电平高低,都会将终端电阻设置为RTT_WR。这个值对于写入数据的完整性和稳定性至关重要。

RTTpark:

RTTpark是当内存没有被激活时的终端电阻值。在DDR4中,当ODT pin被驱动为低电平时,默认的终端电阻值由MR5中的A[8:6]位确定。这个值在内存空闲时起作用,有助于在没有数据传输时减少功耗。

3. Vref DQ Calibration

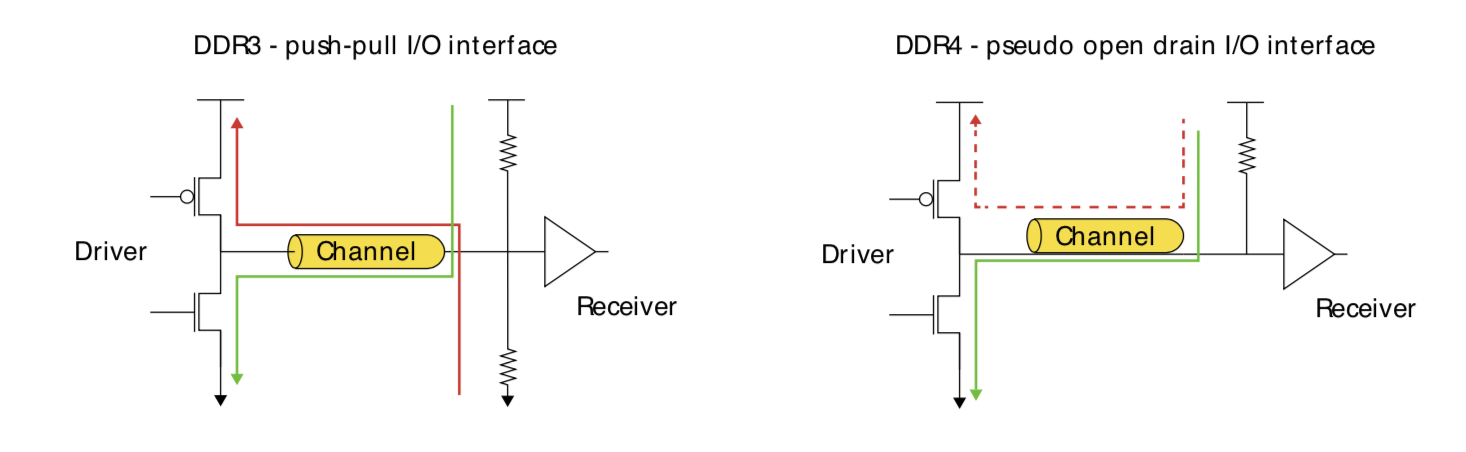

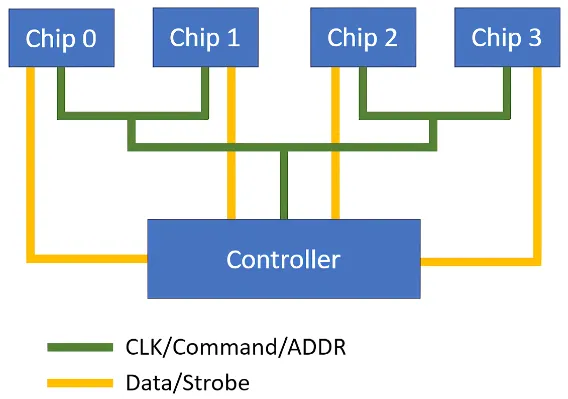

在DDR4中,数据线路(DQ)的端接方式从DDR3的CTT(Center Tapped Termination,也称为SSTL Series-Stud Terminated Logic)更改为POD(Pseudo Open Drain)。这种改变旨在提高高速下的信号完整性,并节省IO功耗。GDDR5(图形DRAM)也采用了POD端接方式。

Vref DQ校准开始时,控制器会发出Vref DQ校准命令。这个命令会触发DRAM内部的校准引擎,调整内部电压基准VrefDQ,直到它与预期的电压水平相匹配。在DDR4中,接收方不再有分压电路,取而代之的是一个内部参考判决电平,判断信号为0或者为1。这个判决电平称为VrefDQ。VrefDQ可以通过模式寄存器MR6进行设定,在VrefDQ校准阶段,控制器需要通过尝试不同的VrefDQ值,来设置一个能够正确区分高低电平的值。

4. Read/Write Training

至此,初始化过程完成,DRAM 处于空闲状态,但内存仍然无法运行。控制器和 PHY 必须执行一些更重要的步骤,然后才能可靠地将数据写入 DRAM 或从 DRAM 中读取。这个重要的阶段被称为读写训练(或内存训练或初始校准)。

对于read/write训练,最常见的是:

- CS Training

- CA Training

- Write Leveling

- Read Centering

- Write Centering

下面举例说明Write Centering是如何training?

写中心化训练(Write Centering)是DDR内存训练过程中的一个关键步骤,其目的是设定每条数据信号线上写数据的发送延迟,以确保DRAM端能够根据对齐数据眼图中央的DQS采样数据信号DQ。以下是写中心化训练的具体操作步骤:

- MPR模式写入(MPR Pattern Write):

在进行写中心化之前,通常会先进行MPR(Multi-Purpose Register)模式写入。DDR4 DRAM包含四个8位可编程寄存器,称为MPR寄存器,用于DQ位训练(即读写中心化)。通过设置模式寄存器MR3[2]为1,启用MPR访问模式。在该模式下,所有向DRAM进行的读写操作都会与MPR进行,而不是真正的存储介质。

- 连续的写和读请求:

在写中心化过程中,控制器会发出一系列的写和读请求。这些请求会逐渐改变数据位的写入延迟,并将读取的数据与写入的数据进行比较。

- 增加写数据时的发送延迟:

控制器会逐渐增加写数据时的发送延迟。这个过程是通过调整写延迟来完成的,以便找到写数据眼图的左右边界。

- 将读取的数据与发送数据进行比较:

控制器会比较读回的数据与写入的数据,以判断在不同的写延迟下数据的准确性。通过这个比较过程,控制器可以确定在正常读写数据时能容忍的最大发送延迟。

- 推断写数据的左右有效边界:

根据比较结果,控制器可以推断出写数据眼图的左边缘和右边缘。利用这些数据,控制器可以将写数据的中央与DQS边沿对齐,确保数据在数据眼图的中央被写入。