RTL仿真无法仿真出CDC 问题或其影响。门级仿真是感知延迟的,但是它们只能在项目的后期执行。

跨时钟域(CDC)路径的终点是触发器,由于时钟的不同步,该触发器可能进入危险的亚稳态。

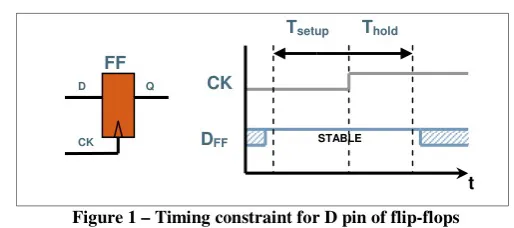

当这些时序不被满足时(即D上的toggle发生在CK边沿太近)时,触发器输出的行为是不可预测的:输出可能是亚稳态,这意味着在0和1之间以一定的水平振荡。这种振荡应该在一定时间后最终稳定在0或1。

在异步设计中,没有办法保证满足setup和hold timing。因此,设计必须能够抵抗这些因素的影响,即避免亚稳态对后续逻辑的影响。

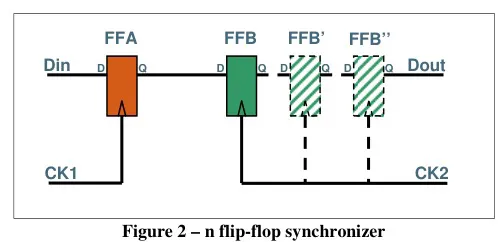

这种结构降低了压稳定在 Dout 上传播的可能性,但无法保证数据正确性。尤其当几个异步信号在CK2时钟域中重新聚合时,这成为一个问题。

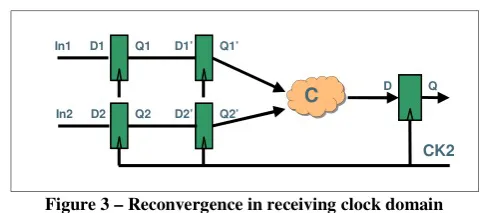

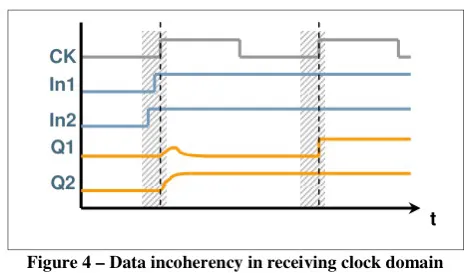

如果 Inl 和 In2 都在 D1 和 D2 上违反 set up/hold 窗口,那么在随后的接收时钟周期中,Ql 和 Q2 可能会变得不稳定。

如果这些重新同步的信号在接收时钟域中会聚,那么在设计阶段必须特别注意处理这些不一致的数据。这必须经过验证。

而这种不一致在RTL前仿真是无法感知的。下面这篇文章给出了它的解决方案。

答案是建模相应的跨时钟域的行为,然后收集功能覆盖率。

下载地址