- 说明

- 点击数:1706

关于三极管

简单讲解一下三极管,如果三极管工作在饱和区(完全导通),Rce≈0,Vce≈0.3V,且这个0.3V,我们就认为它直接接地了。那么就需要让Ib大于等于1mA,若Ib=1mA, Ic=100mA,它的放大倍数β=100,三极管完全导通。如下图,是一个NPN三极管。

- 说明

- 点击数:1034

电路检测电路常用于:高压短路保护、电机控制、DC/DC换流器、系统功耗管理、二次电池的电流管理、蓄电池管理等电流检测等场景。

- 说明

- 点击数:1200

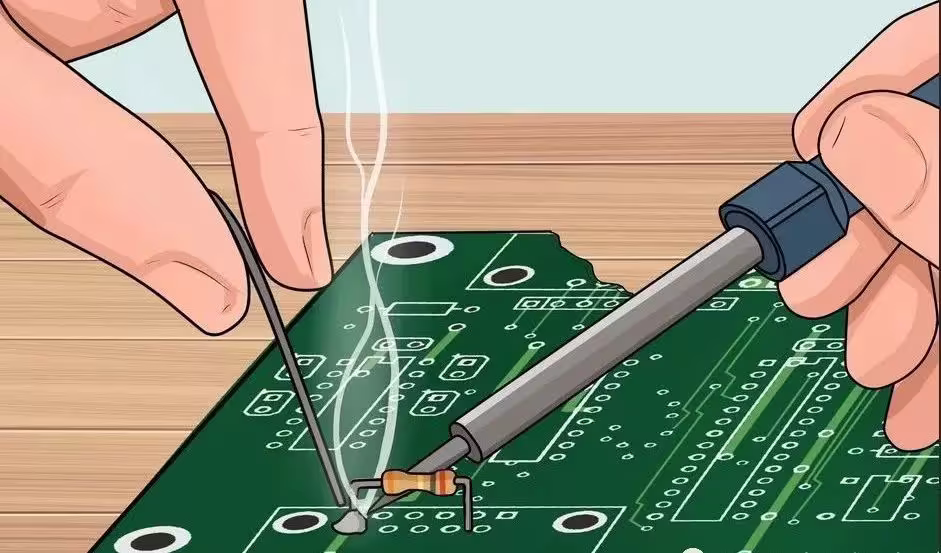

回前两天画了一个功率板子,但是由于走线的线径太细,因此在上电的一瞬间一根电线被立即烧断。为了解决这个问题,我们最后只能通过外部飞线的方式来替换烧断的电线。

- 说明

- 点击数:1118

模拟电路的设计是工程师们最头疼,但也是最致命的设计部分。尽管目前数字电路、大规模集成电路的发展非常迅猛,但是模拟电路的设计仍是不可避免的,有时也是数字电路无法取代的,例如RF射频电路的设计。

本文总结了模拟电路设计中应该注意的问题。

- 说明

- 点击数:1055

电感器俗称电感,本质上是一个线圈,有空心线圈也有实心线圈,实心线圈有铁芯或者其它材料制成的芯,电感的单位是“H”,简称“亨”。此外,更小的单位是mH,uH,换算方式为1H=1000mH=1000000uH。

电感的常见作用

阻交通直

对于直流电,电感是相当于短路的;而对于交流电,电感是对其有阻碍作用的,交流电的频率越高,电感对它的阻碍作用越大。

© 2026 VxWorks Club