- 说明

- 点击数:2540

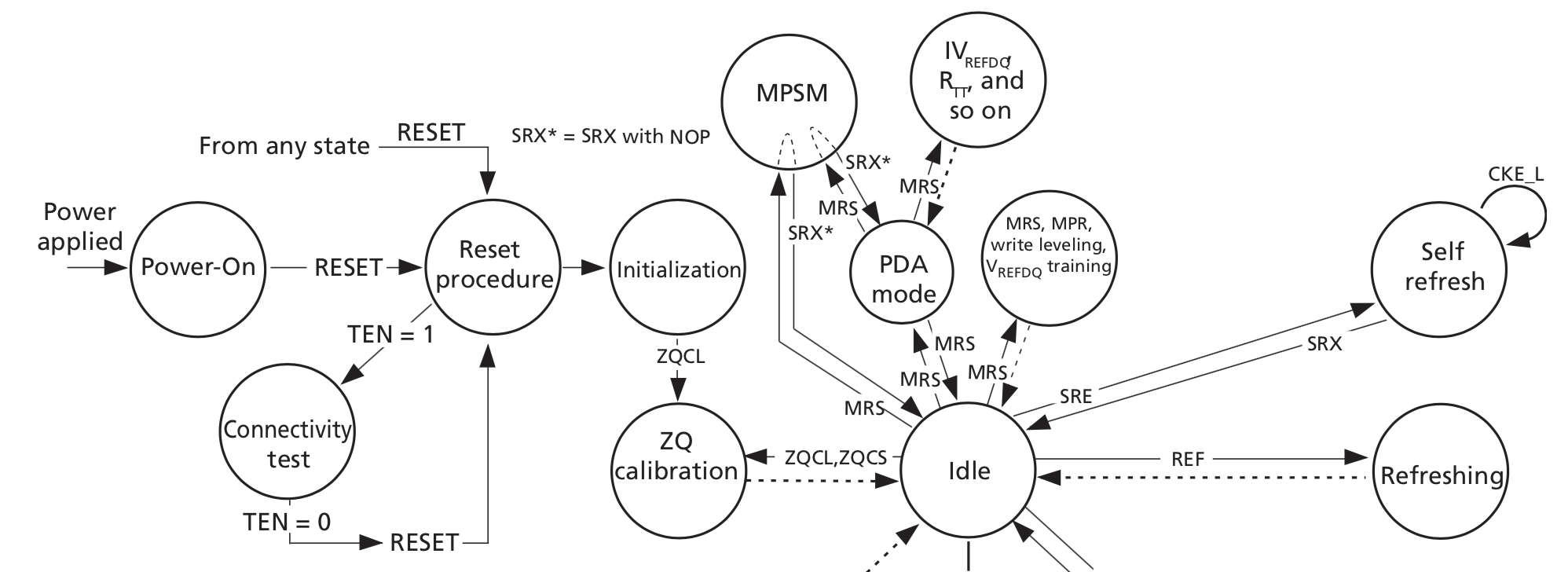

DDR4内存的初始化过程是确保内存模块能够高效、稳定运行的关键步骤。这个过程主要包括以下四个阶段:

- Power-up and Initialization

- ZQ Calibration

- Vref DQ Calibration

- Read/Write Training (a.k.a Memory Training or Initial Calibration)

1. Power-up and initialization

上电与初始化是由一系列精心设计的步骤组成的序列(sequence)。一般来说,在系统上电之后,ASIC/FPGA/处理器中的 DDR 控制器会被从复位状态中释放,自动执行上电与初始化序列。

- 说明

- 点击数:2012

在超大规模集成(VLSI)设计中,“buffer”是基本组件,对芯片的性能和信号完整性产生重大影响。让我们揭开buffer的复杂性,了解其功能,并深入研究它们在芯片设计领域的多样化应用。

从本质上讲,芯片设计中的buffer是放大信号强度的电路。与其他放大器不同,buffer旨在保持信号波形的完整性,同时增强其驱动能力。它们是克服信号传播延迟相关问题不可或缺的工具,以确保数字电路不同部分之间的高效通信。

- 说明

- 点击数:1400

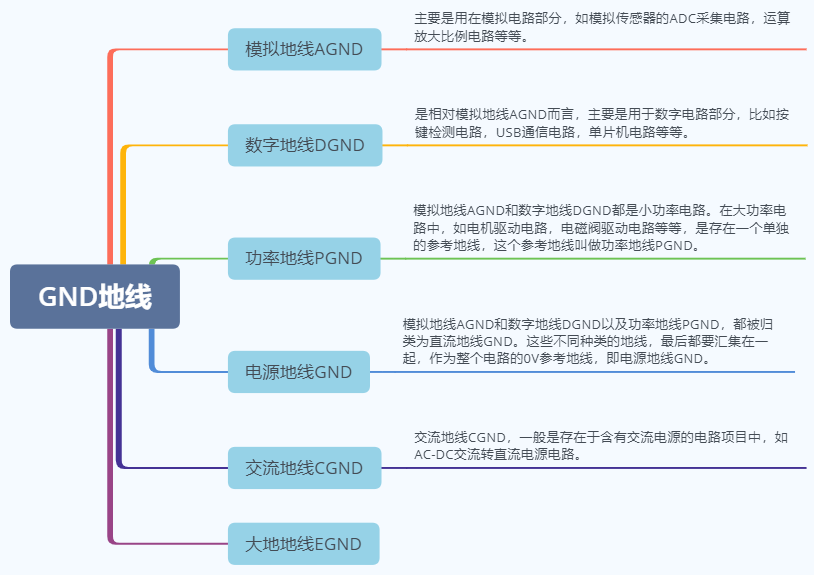

在电路原理设计阶段,为了降低电路之间的互相干扰,工程师一般会引入不同的GND地线,作为不同功能电路的0V参考点,形成不同的电流回路。

GND地线的分类

细究GND的原理

一个地线GND怎么会有这么多区分,简单的电路问题怎么弄得这么复杂?为什么需要引入这么多细分的GND地线功能呢?工程师一般针对这类GND地线设计问题,都简单的统一命名为GND,在原理图设计过程中没有加以区分,导致在PCB布线的时候很难有效识别不同电路功能的GND地线,直接简单地将所有GND地线连接在一起。虽然这样操作简便,但这将导致一系列问题:

- 说明

- 点击数:1364

时钟域交叉(CDC)是指用于在ASIC IC或FPGA中管理数字系统内不同时钟域之间的数据传输的技术。下图1显示了CDC的场景。在这里,来自时钟域A的数据被传输到时钟域B。时钟A和时钟B可以具有不同的频率以及不同的相位。因此,两个时钟域彼此异步。

- 说明

- 点击数:2635

相信大家在做PCB设计时,都会发现布线这个环节必不可少,而且布线的合理性,也决定了PCB的美观度和其生产成本的高低,同时还能体现出电路性能和散热性能的好坏,以及是否可以让器件的性能达到最优等。

本篇内容,将针对PCB的布线方式,做个全面的总结。

1、走线长度应包含过孔和封装焊盘的长度。

2、布线角度优选135°角出线方式,任意角度出线会导致制版出现工艺问题。

© 2026 VxWorks Club