- 说明

- 点击数:1935

在DC-DC芯片的应用设计中,PCB布板是否合理对于芯片能否表现出其最优性能有着至关重要的影响。

不合理的PCB布板会造成芯片性能变差如线性度下降(包括输入线性度以及输出线性度)、带载能力下降、工作不稳定、EMI辐射增加、输出噪声增加等,更严重的可能会直接造成芯片损坏。

一般DC-DC芯片的使用手册中都会有其对应的PCB布板设计要求以及布板示意图,本次我们就以同步BUCK芯片为例简单讲一讲关于DC-DC芯片应用设计中的PCB Layout设计要点。

1、关注芯片工作的大电流路径

DC-DC芯片布板需遵循一个非常重要的原则,即开关大电流环路面积尽可能小。下图所示的BUCK拓补结构中可以看到芯片开关过程中存在两个大电流环路。

红色为输入环路,绿色为输出环路。每一个电流环都可看作是一个环路天线,会对外辐射能量,引起EMI问题,辐射的大小与环路面积呈正比。

- 说明

- 点击数:1616

最容易访问的设备是什么

是内存!

要读写内存,知道它的地址就可以:

volatile unsigned int *p = 某个地址;

unsigned int val;

*p = val; /* 写 */

val = *p; /* 读 */

只有内存能这样简单、方便地使用吗?

不是的,所有的"ram-like"接口设备都可以这样操作。

什么叫"ram-like"接口?

- 说明

- 点击数:1606

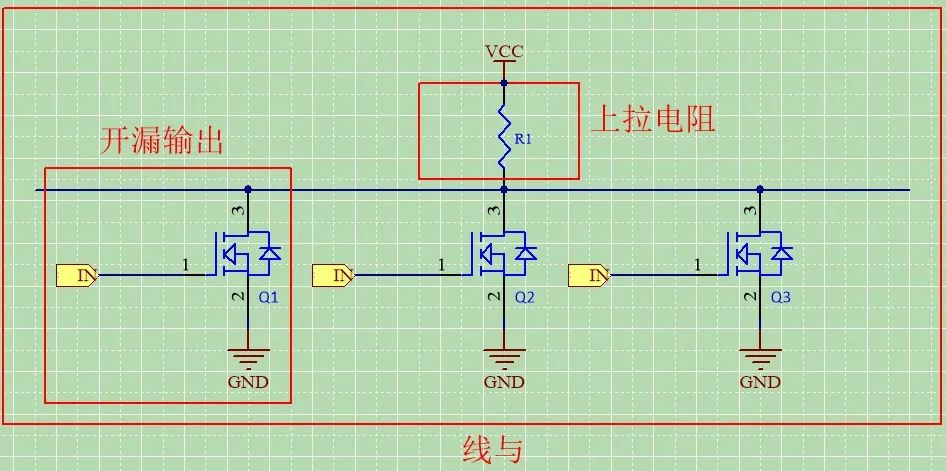

I2C为什么要接上拉电阻?因为它是开漏输出。

为什么是开漏输出?

I2C协议支持多个主设备与多个从设备在一条总线上,如果不用开漏输出,而用推挽输出,会出现主设备之间短路的情况。所以总线一般会使用开漏输出。

- 说明

- 点击数:3067

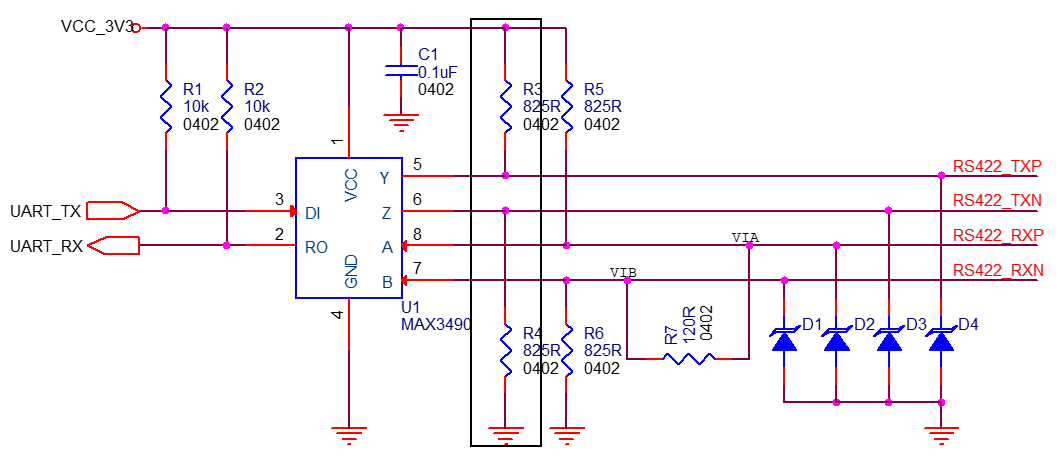

1 典型的RS422接口电路

图 1 典型的RS422接口电路

- 说明

- 点击数:1531

我打算写几篇有关计算机内部的文章,以期能够解释清楚现代内核的工作原理。对这些事物感兴趣的爱好者和程序员往往缺乏经验,我希望对这些人能有所帮助。我们把重点放在 Linux,Windows 和 Intel 处理器上。探究内部构造是我的一个爱好,我曾经写过了很多运行在内核模式(kernel mode)下的代码,但是有很长时间没写过了,第一篇文章就让我们来描述下基于 Intel 的主板结构布局、CPU 如何访问内存以及系统内存映射吧。

© 2026 VxWorks Club