- 说明

- 点击数:2643

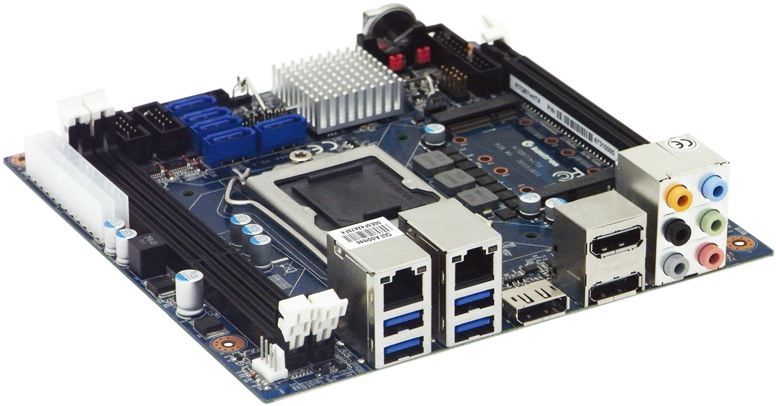

Motherboards

RT Embedded offers a broad range of high quality longevity motherboards from Mini-ITX to full size ATX, covering Embedded and Server market. This variety of motherboards serves the different needs of our customers in almost all applications. These motherboards are based on newest processors and chipset platforms, and utilize Intel advanced technology components.

- 说明

- 点击数:2795

基于龙芯平台的PMON研究与开发

下载地址

摘要:

在嵌入式软件系统开发中,为了能够快速正确地引导操作系统,需要有一个功能强大的Bootloader来支持。PMON是一种针对嵌入式系统而开发的操作系统引导程序,其作用在于初始化嵌入式硬件系统的外设以便能够正确引导、启动操作系统。基于PMON开发移植的目的,从研究PMON的架构出发,深入研究PMON的编译环境及其执行流程,在此基础上,通过向PMON中添加网卡驱动代码,并验证了网卡驱动工作的正确性,最终实现了PMON下的网卡驱动移植。

- 说明

- 点击数:1994

基于SOPC基本信号产生器的设计与实现

下载地址

基于SOPC基本信号产生器的设计与实现

Synopsis

This paper introduces a basic signal generator based on the SOPC design technology.In order to achieve the basic signal generator,the design of system hardware circuit takes EP1C6Q240C8of Altera Corporation as the hardware core,embeds the soft-core CPU into FPGA-chip,and unifies the memory circuit,high-speed DAC circuit,LCD circuit,the keyboard circuit,JTAG configuration circuit,the power circuit and so on.The paper describes the main module design and gives some pictures for hardware and software test.Through the oscilloscope observation,system design requirements are met and the desired objectives are achieved.

- 说明

- 点击数:2408

基于龙芯2F架构的PMON分析与优化

下载地址

基于龙芯2F架构的PMON分析与优化

摘要:

基本输入/输出系统(BIOS)是现代计算机系统的重要组成部 分,负责计算机系统的开机自检、板级初始化、加载操作系统内核以及基本I/O功能.以龙芯2F CPU架构为研究背景,在其基础上分析了PMON的系统结构与工作流程,通过添加网络驱动程序,最终实现通过PMON加载Linux和VxWorks操作 系统.进行必要的功能完善与性能优化,并经过严格的测试以排除可能存在的深层次缺陷,实现了一个性能稳定、功能完善、高可靠性的能与国产龙芯2F处理器平 台紧密搭配的BIOS.

- 说明

- 点击数:2073

基于OpenCL的均值平移算法在多个众核平台的性能优化研究

下载地址

基于OpenCL的均值平移算法在多个众核平台的性能优化研究

摘要:

OpenCL作为一种面向多种平台、通用目的的编程标准,已经对许多应用程序进行了加速。由于平台硬件和软件环境的差异,通用的优化方法不一定在所有平台都有很好的加速。通过对均值平移算法在GPU和APU平台的优化,探讨了不同平台各种优化方法的贡献力,一方面研究各个平台的计算特性,另一方面体会不同优化方法的优劣,在优劣的相互转化中寻求最优的解决方案。实验表明,算法并行优化前、后在AMD 5850、Tesla C2050和APU A6-3650上分别达到了9.68、5.74和1.27倍加速,并行相比串行程序达到79.73、93.88和2.22倍加速,前两个平台OpenCL版本相比,CUDA版本的OpenCV程序达到1.27和1.24倍加速。

© 2026 VxWorks Club